# **OMAP35x SOM-LV Hardware Specification**

### Hardware Documentation

Logic PD // Products Published: June 2008

Last Revised: December 2017

This document contains valuable proprietary and confidential information and the attached file contains source code, ideas, and techniques that are owned by Logic PD, Inc. (collectively "Logic PD's Proprietary Information"). Logic PD's Proprietary Information may not be used by or disclosed to any third party except under written license from Logic PD, Inc.

Logic PD, Inc. makes no representation or warranties of any nature or kind regarding Logic PD's Proprietary Information or any products offered by Logic PD, Inc. Logic PD's Proprietary Information is disclosed herein pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipment. The only warranties made by Logic PD, Inc., if any, with respect to any products described in this document are set forth in such license or agreement. Logic PD, Inc. shall have no liability of any kind, express or implied, arising out of the use of the Information in this document, including direct, indirect, special or consequential damages.

Logic PD, Inc. may have patents, patent applications, trademarks, copyrights, trade secrets, or other intellectual property rights pertaining to Logic PD's Proprietary Information and products described in this document (collectively "Logic PD's Intellectual Property"). Except as expressly provided in any written license or agreement from Logic PD, Inc., this document and the information contained therein does not create any license to Logic PD's Intellectual Property.

The Information contained herein is subject to change without notice. Revisions may be issued regarding changes and/or additions.

© Copyright 2017, Logic PD, Inc. All Rights Reserved.

# **Revision History**

| REV | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCHEMATIC<br>PN & REV       | APPROVAL  | DATE     |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|----------|

| 1   | Internal Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1007969<br>Rev 8            | NJK       | 04/28/08 |

| A   | -Throughout: Updated Triton2 name to TPS65950; -Section 3: Added note about regulators; -Section 4.2.1: Updated memory options; -Sections 4.4, 4.5, & 4.9: Updated component part numbers; -Section 7.1: Changed max voltage for touch screen signals to 3.1 V -Section 5.2: Added note about SIM interface for respective signal descriptions; -Section 6: Clarified measurement tolerances -Section 6: Updated diagram so that it only shows footprint for SOM-LV Type III                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1007969<br>Rev 8            | NJK       | 06/05/08 |

| В   | -Added standard document cover page; updated header and footer layout; -Figure 2.2: Removed USB HS OTG signal coming from USB PHY x1; -Table 3.1: Added voltage ratings for 5V supply; the current values were given in Amps when they should be in mA, this has been corrected; Removed note about regulators; -Section 4.9 & throughout: USB host can only operate in high-speed; -Section 5.4: Added MSTR_nRST signal to JTAG interface explanation; -Section 5.6.1: Added note about USB1_VBUS powering the SOM; -Section 6: For nCS2 chip select, removed the word "boot" from the device fieldSection 7.1: Pin J1.153 was "RFU", updated to "LCD_DON"; -Section 7.2: Pin J2.44 changed parenthetical net name from "VIO_1V8" to "uP_LA12"; pins J2.156, 158, 160, 162, 164, & 166 updated descriptions to explain GPIO is not available when Bluetooth is populated; pinJ2.168 updated description by removing the words "boot" and "bootselect"; added note about uP_nCS0 tied to uP_nCS2; pins J2.237-240 updated signal names used for test, used to be listed as "RFU"; for "CSI1_xxx" signals, updated the description to indicate that the Camera Serial Interface is not natively supported on the OMAP35x processor; -Section 0: Added section for Wireless Antenna Connectors; Updated Mechanical Drawings | 1009917<br>Rev A            | NJK & JCA | 09/08/08 |

| С   | -Sections 4.4 & 4.5: Specified wireless antenna connector locations on PCB;<br>-Section 6: Added note about chip select memory locations<br>-Section 7.1: Corrected J1 connector processor data bits to be I/O signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1009917<br>Rev A            | NJK       | 10/29/08 |

| D   | - Figure 2.2: Updated Block Diagram; - Added Section 4.2.3.1: Example CompactFlash Timing; - Section 4.9: Updated for new USB host controller, which adds USB high-speed ports that support more than high-speed mode; - Section 4.13: Added design note about the GPMC bus; - Section 6: Added nCS6 to table - Section 7.1: Updated voltages on pins J1.37, 39 for USB changes; Updated descriptions for pins J1.131 & 133; pin J1.135 changed from uP_DREQ1 to RFU; pins J1.141, 143, 145, & 147 were updated to include nCS4/nCS5; pins J1.174, 176, & 178 updated description; pins J1.233, 235, 237, 239, & 240 changed from RFU to used for testing; - Section 7.2: Pins J2.58, 60, 62, 64, 70, 74, 76, & 78 changed from RFU to being used by new USB features; pin J2.87 added Note 1 at the conclusion of table; pin J2.175 added required capacitance note;                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1010913<br>Rev B            | NJK       | 01/20/09 |

| Е   | <ul> <li>Section 2.2: Used updated look for block diagram;</li> <li>Section 3: Added Extended Temperature range; corrected dimensions;</li> <li>Section 5.2.1: Added Important Note that MSTR_nRST does not reset PMIC;</li> <li>Section 5.5: Added Important Note about ETM interface speeds;</li> <li>Section 7.1: J1.23,37 &amp; J2.58,70 noted external 10K pull-up resistor to 3.3V requirement for all nOC pins;</li> <li>Added Section 2.3.3;</li> <li>Appendix A: Updated drawing</li> <li>Section 7: Added Important Note concerning power rails for GPIOs;</li> <li>Section 7.2: J2.181, 183, 185, 187 changed to GPI only; J2.133, 135 added</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1010913<br>Rev C<br>1010913 | JCA       | 09/02/09 |

| F   | can be used as GPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Rev C                       | BSB & NJK | 10/26/09 |

| REV | REVISION DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SCHEMATIC<br>PN & REV | APPROVAL | DATE     |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|----------|

| G   | - Section 3: Updated DC 5 V Voltage Min & Typical numbers; Added notes 7-9 to explain how the power numbers were obtained; - Section 4.8.5.1: Added list of reserved I2C addresses; - Section 7: Updated important note to remove reference to LogicLoader; - Section 7.1: J1.113, 115 added notes about signals used with SD cards; - Section 7.2: J2.133, 135, 181, 183, 185, 187 changed voltage to reference VAUX4 and updated Notes; J2.233 added note that this signal is shared with Bluetooth;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1010913<br>Rev C      | RH & NJK | 04/21/10 |

| Н   | - Section 3: Added 802.11 numbers; Added numbers for Active Current running WinCE BSP; Updated typical numbers for active currents; Updated extended temperature range; - Section 4.3: Added note about baseboard Ethernet socket contains integrated magnetics; - Section 4.4: Added information for the Murata module; - Section 4.9: Added information about USB transceiver; - Sections 4.11 & 4.13: Added design note; - Section 6: Removed nCS6 from chip select table; - Section 7: Added notes for specific PoP signals; Organized notes and moved several multi-signal notes to end of tables instead of in descriptions; - Section 7.1: Updated descriptions for J1.23, 25; Corrected voltage level and updated descriptions for J1.37, 39; Changed pins J1.233, 235, 239, & 240 to use used as Wireless signals instead of SPI_*; - Section 7.2: Corrected voltage level and updated descriptions for J2.58, 60, 70, 78; Changed pins J2.81, 83 to RFU; Updated description for pin J2.175 | 1014465<br>Rev A      | NJK      | 11/03/10 |

| I   | -Section 3, 7.1, & 7.2: Changed Max DC Main Battery Input Voltage to 4.3V as a result of the wireless module limits; -Section 4.9: Revised incorrect USB reference; -Section 5.6.1.3: Added Important Note about 3.3V rail required for Ethernet and USB; -Section 7.1 & 7.2 Added BGA Ball # and Processor Signal columns to tables -Section 2.3.2: Added antenna part number included in dev kit; Added separate table for connector information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1014465<br>Rev A      | NJK      | 09/12/11 |

| J   | -Appendix A: Added updated mechanical drawing that includes connector pin orientations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1014465<br>Rev A      | SO       | 06/19/12 |

| К   | -Throughout: Updated template; updated links for new support site; reorganized several sections; -Section 4.9: Added note that proper USB adapter cable is necessary for USB 2.0 OTG to function as host; added link to Digi-Key adapter cable that supports host function; -Section 7.2: Changed I/O column to output only and added <i>open drain</i> to descriptions for J2:93, J2:95, J2:97, J2:99, J2:101, J2:103, J2:105, J2:107; changed I/O column to input only for J2:109, J2:113, J2:115, J2:117, J2:119, J2:121, J2:123, J2:125, J2: 151, J2:153, J2:155, J2:157, J2:171, J2:181, J2:183, and J2:187                                                                                                                                                                                                                                                                                                                                                                                      | 1014465<br>Rev B      | SO, BSB  | 11/14/13 |

| L   | - <u>Section 4.2.2</u> : Documented change from 8MB Strataflash NOR to 16MB NOR Embedded Memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1028918<br>Rev A-0    | JMC      | 08/23/17 |

Please check the  $\underline{\text{Logic PD support site}}^1$  for the latest revision of this specification and additional documentation.

PN 1009954L

<sup>&</sup>lt;sup>1</sup> http://support.logicpd.com/Home.aspx

# **Table of Contents**

| 1 |    |         | uction                                                      |    |

|---|----|---------|-------------------------------------------------------------|----|

|   | 1. |         | duct Overview                                               |    |

|   | 1. | .2 Abb  | reviations, Acronyms, and Definitions                       | 1  |

|   | 1. | .3 Sco  | pe of Document                                              | 2  |

|   | 1. | .4 Add  | itional Documentation and Resources                         | 2  |

| 2 |    |         | onal Specification                                          |    |

|   |    |         | AP35x Processor Highlights                                  |    |

|   |    |         | 1-LV Interface                                              |    |

|   |    |         | hanical Specification                                       |    |

|   | _  |         | Interface Connectors                                        |    |

|   |    |         | Wireless Antenna Connectors                                 |    |

|   |    |         | Mounting Specifications                                     |    |

|   |    |         | OMAP35x SOM-LV Mechanical Drawings                          |    |

| 2 |    |         | cal Specification                                           |    |

| 3 |    | Dorinh  | eral Specification                                          | 0  |

| 4 |    |         | cks                                                         |    |

|   |    |         |                                                             |    |

|   | 4  |         | nory                                                        |    |

|   |    |         | Package-on-Package Memory (Mobile DDR and NAND)             |    |

|   |    |         | NOR Flash                                                   |    |

|   |    |         | PC Card Interface                                           |    |

|   |    | 4.2.3.  | i rii ii rii ii rii ii J                                    |    |

|   |    |         | 100 Ethernet PHY                                            |    |

|   |    |         | .11 Wireless Ethernet                                       |    |

|   |    |         | etooth                                                      |    |

|   |    |         | io Codec                                                    |    |

|   |    |         | play Interface                                              |    |

|   | 4  | .8 Seri | al Interfaces                                               | 14 |

|   |    |         | UARTA                                                       |    |

|   |    |         | UARTB                                                       |    |

|   |    | 4.8.3   | UARTC                                                       | 15 |

|   |    | 4.8.4   | McSPI                                                       | 15 |

|   |    |         | I2C                                                         |    |

|   |    | 4.8.5.  |                                                             |    |

|   | 4  | .9 USF  | 3 Interface                                                 |    |

|   |    |         | C/Touch Interface                                           |    |

|   |    |         | eral Purpose I/O                                            |    |

|   |    |         | poard Logic Interfaces                                      |    |

|   |    |         | ansion/Feature Options                                      |    |

| 5 |    |         | 1 Integration                                               |    |

| • |    |         | figuration                                                  |    |

|   | _  |         | ets                                                         |    |

|   | ,  |         | Master Reset (MSTR_nRST)—Reset Input                        |    |

|   |    |         | OMAP35x SOM-LV Reset (RESET_nOUT/SYS_nRESWARM)—Reset output |    |

|   | _  |         |                                                             |    |

|   |    |         | errupts                                                     |    |

|   |    |         | G Debugger Interface                                        |    |

|   |    |         | Adapter Interface                                           |    |

|   | 5  |         | ver Management                                              |    |

|   |    |         | System Power Supplies                                       |    |

|   |    | 5.6.1.  |                                                             |    |

|   |    | 5.6.1.  |                                                             |    |

|   |    | 5.6.1.  |                                                             |    |

|   |    | 5.6.1.  | <b>-</b>                                                    |    |

|   |    |         | System Power Management                                     |    |

|   |    | 5.6.3   | Microcontroller                                             | 21 |

|   |    | 5.6.3.  | 1 Run State                                                 | 21 |

|   |    | 5.6.3.  | 2 Suspend State                                             | 22 |

|   |    | 5.6.3.  | 3 Standby State                                             | 22 |

### **OMAP35x SOM-LV Hardware Specification**

| 5.7 ESD Considerations                |  |

|---------------------------------------|--|

| 6 Memory & I/O Mapping                |  |

| 7 Pin Descriptions and Functions      |  |

| 7.1 J1 Connector 240-Pin Descriptions |  |

| 7.2 J2 Connector 240-Pin Descriptions |  |

| Appendix A: Mechanical Drawings       |  |

# **Table of Figures**

| Figure 2.1: OMAP35x Processor Block Diagram                      |    |

|------------------------------------------------------------------|----|

| Figure 2.2: OMAP35x SOM-LV Block Diagram                         | 5  |

| Figure 4.1: CompactFlash Read Timing                             |    |

| Figure 4.2: CompactFlash Write Timing                            |    |

| Table of Tables                                                  |    |

| Table 2.1: Baseboard Mating Connectors                           | 6  |

| Table 2.2: Antenna PCB Connectors                                | 6  |

| Table 2.3: Antennas Included in Development Kit                  | 6  |

| Table 2.4: Support Spacers to Secure OMAP35x SOM-LV to Baseboard | 6  |

| Table 3.1: Absolute Maximum Ratings                              | 8  |

| Table 3.2: Recommended Operating Conditions                      |    |

| Table 4.1: Processor Clock Specifications                        |    |

| Table 6.1: Chip Select Signals                                   | 22 |

#### 1 Introduction

#### 1.1 **Product Overview**

The OMAP35x System on Module (SOM) is a compact, product-ready hardware and software solution that fast forwards embedded designs.

Based on the Texas Instruments (TI) OMAP35x processor and designed in the SOM-LV Type III form factor, the OMAP35x module offers essential features for handheld and embedded networking applications.

The SOM-LV is an off-the-shelf solution that reduces development risks associated with the complex design and manufacturing details of the OMAP 3 processor. The standard SOM-LV form factor allows developers to reuse existing baseboard designs when upgrading to new OMAP processors, which extends roadmap possibilities for their end-product. By starting with the corresponding Zoom™ OMAP35x Development Kit, engineers can write application software on the same hardware that will be used in the final product.

The OMAP35x SOM-LV is ideal for applications in the medical, point-of-sale, industrial, gaming, and security markets. From patient monitoring and medical imaging, to card payment terminals and bar code readers, to CCTV cameras and intruder alarms, the OMAP35x SOM-LV allows for powerful versatility and long-life products.

NOTE: Within this document, OMAP35x is used to denote any TI OMAP processor from the OMAP35x family (i.e., OMAP3530, OMAP3525, OMAP3515, and OMAP3503).

#### 1.2 **Abbreviations, Acronyms, and Definitions**

| ADC | Analog to Digital Converter |

|-----|-----------------------------|

| BSP | Board Support Package       |

| BTB | Board-to-Board              |

| DDR | Double Data Rate (RAM)      |

| DMA | Direct Memory Access        |

ESD Electrostatic Discharge FIFO First In First Out

GPIO General Purpose Input Output General Purpose Memory Controller **GPMC**

GPO General Purpose Output Inter-Integrated Circuit I2C Inter-Integrated Circuit Sound I2S

**Integrated Circuit** IC I/O Input/Output IRQ Interrupt Request Liquid Crystal Display LCD LDO Low Dropout (Regulator)

McBSP Multi-channel Buffered Serial Port

OTG On-the-Go (USB) PCB Printed Circuit Board

Personal Computer Memory Card International Association (PC Cards) PCMCIA

PHY Physical Layer PLL Phase Lock Loop POP Package On Package PWM Pulse Width Modulation

RTC Real Time Clock

SDIO Secure Digital Input Output

SDRAM Synchronous Dynamic Random Access Memory

SOM System on Module SSP Synchronous Serial Port

SPI Standard Programming Interface

STN Super-Twisted Nematic (LCD)

TFT Thin Film Transistor (LCD)

TI Texas Instruments

TSC Touch Screen Controller

TTL Transistor-Transistor Logic

UART Universal Asynchronous Receive Transmit

### 1.3 Scope of Document

This hardware specification is unique to the design and use of the OMAP35x SOM-LV as designed by Logic PD and does not intend to include information outside of that scope. Detailed information about the TI OMAP35x processors or any other device component on the SOM can be found in their respective manuals and specification documents.

#### 1.4 Additional Documentation and Resources

The following documents and documentation resources have been referenced throughout this hardware specification:

- TI's <u>OMAP35x Technical Reference Manual (TRM)</u><sup>2</sup>

- TI's OMAP3530/25 Applications Processor Datasheet<sup>2</sup>

- TI's TPS65950 OMAP Power Management and System Companion Device TRM<sup>3</sup>

- TI's <u>TPS65950 Data Manual</u><sup>3</sup>

- TI'S TSC2004 Datasheet<sup>4</sup>

- <u>USB 2.0 Specification</u><sup>5</sup> available from USB.org

- Logic PD's LogicLoader v2.4 User Manual<sup>6</sup>

- Logic PD's OMAP35x SOM-LV LogicLoader User Manual Addendum<sup>7</sup>

- Logic PD's <u>AN 388 OMAP35x SOM-LV Power Management</u><sup>8</sup>

- Logic PD's Hardware Design Files (BOM, Schematic, and Layout) for all boards included in the development kit (baseboard, SOM, LCD), as well as all standard configuration SOMs. Sign into your account on <u>Logic PD's support site</u><sup>9</sup> to access these files.

<sup>&</sup>lt;sup>2</sup> http://www.ti.com/product/omap3530

<sup>&</sup>lt;sup>3</sup> http://www.ti.com/product/tps65950#technicaldocuments

<sup>4</sup> http://www.ti.com/product/tsc2004

<sup>&</sup>lt;sup>5</sup> http://www.usb.org/developers/docs/

<sup>6</sup> http://support.logicpd.com/DesktopModules/Bring2mind/DMX/Download.aspx?portalid=0&EntryId=1455

<sup>7</sup> http://support.logicpd.com/DesktopModules/Bring2mind/DMX/Download.aspx?portalid=0&EntryId=1126

<sup>8</sup> http://support.logicpd.com/DesktopModules/Bring2mind/DMX/Download.aspx?portalid=0&EntryId=1108

<sup>9</sup> http://support.logicpd.com/Home.aspx

# 2 Functional Specification

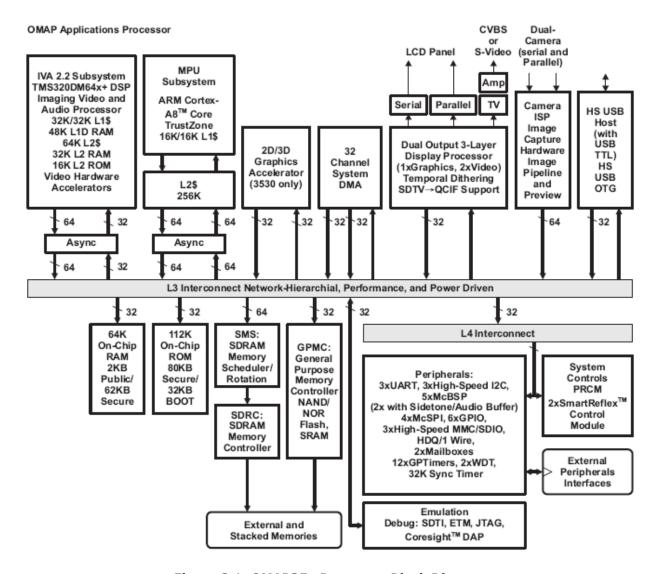

### 2.1 OMAP35x Processor Highlights

The OMAP35x SOM-LV uses TI's high-performance OMAP35x processor. This device features the Superscalar ARM® Cortex $^{TM}$ -A8 RISC core and provides many integrated on-chip peripherals, including:

- Superscalar ARM® Cortex™-A8 RISC core

Vectored floating point unit

16 Kbytes instruction L1 cache

16 Kbytes data L1 cache

256 Kbyte L2 cache

64 Kbyte RAM

32 Kbyte ROM

Integrated LCD Controller

Up to 1024 x 768 x 24 bit color

Three UARTs

12S codec interface

One high-speed USB 2.0 On-the-Go (OTG) interface and one high-speed USB 2.0 host interface

Many general purpose I/O (GPIO) signals

- See TI's OMAP35x TRM and OMAP3530/25 Applications Processor Datasheet for additional information.

**IMPORTANT NOTE:** Please visit <u>TI's website</u><sup>10</sup> for errata on the OMAP35x processor.

Programmable timers

Real time clock (RTC)

Low power modes

\_

<sup>10</sup> http://www.ti.com/product/omap3530

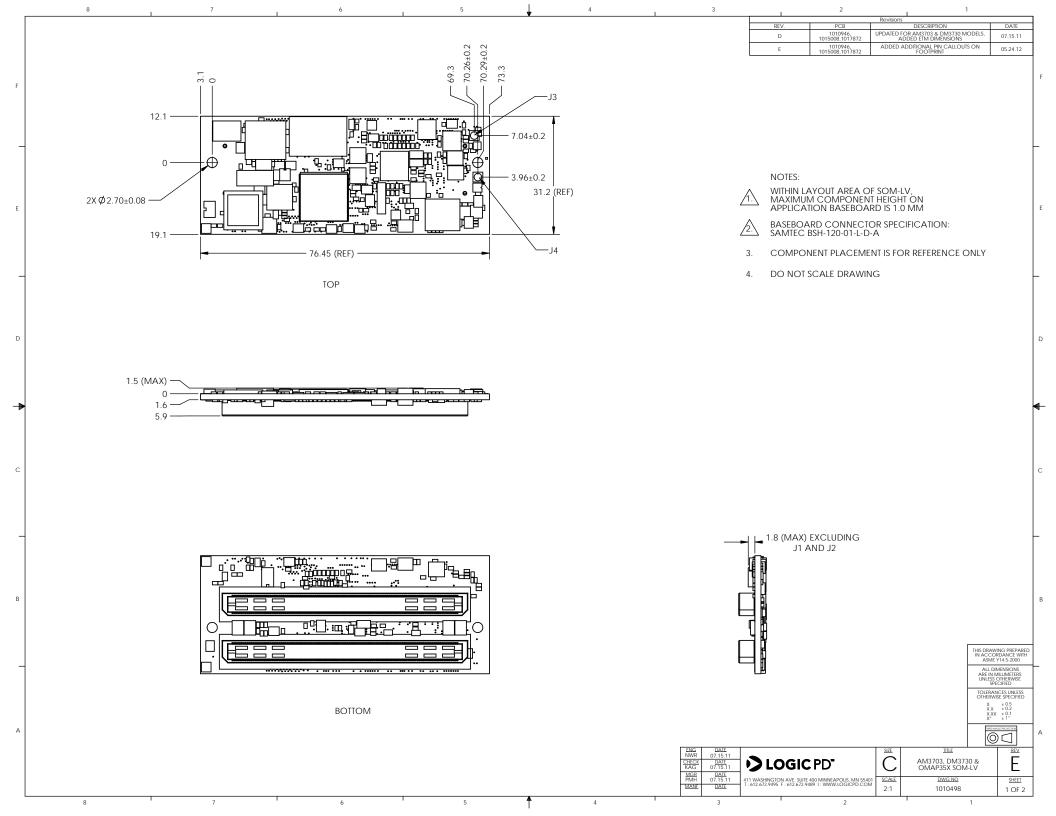

Figure 2.1: OMAP35x Processor Block Diagram

**NOTE:** The block diagram pictured above comes from TI's *OMAP3530/25 Applications Processor Datasheet.*

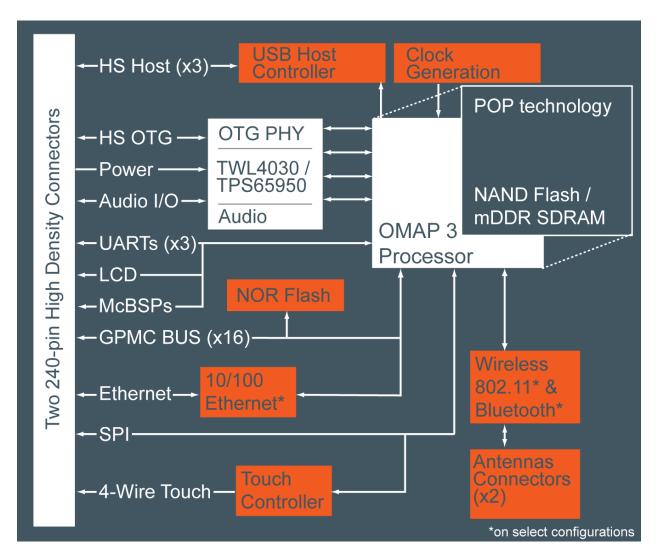

### 2.2 SOM-LV Interface

Logic PD's common SOM-LV interface allows for easy migration to new processors and technology. Logic PD is constantly researching and developing new technologies to improve performance, lower cost, and increase feature capabilities. By using the common SOM-LV footprint, it is possible to take advantage of Logic PD's work without having to re-spin the old design in certain cases dependent upon peripheral usage.

In fact, encapsulating a significant amount of your design onto the SOM-LV reduces any long-term risk of obsolescence. If a component on the SOM-LV design becomes obsolete, Logic PD will simply design for an alternative part that is as transparent to your product as possible. Furthermore, Logic PD tests all SOMs prior to delivery, decreasing time-to-market

and ensuring a simpler and less costly manufacturing process.  $\underline{\text{Contact Logic PD}}^{11}$  for more information.

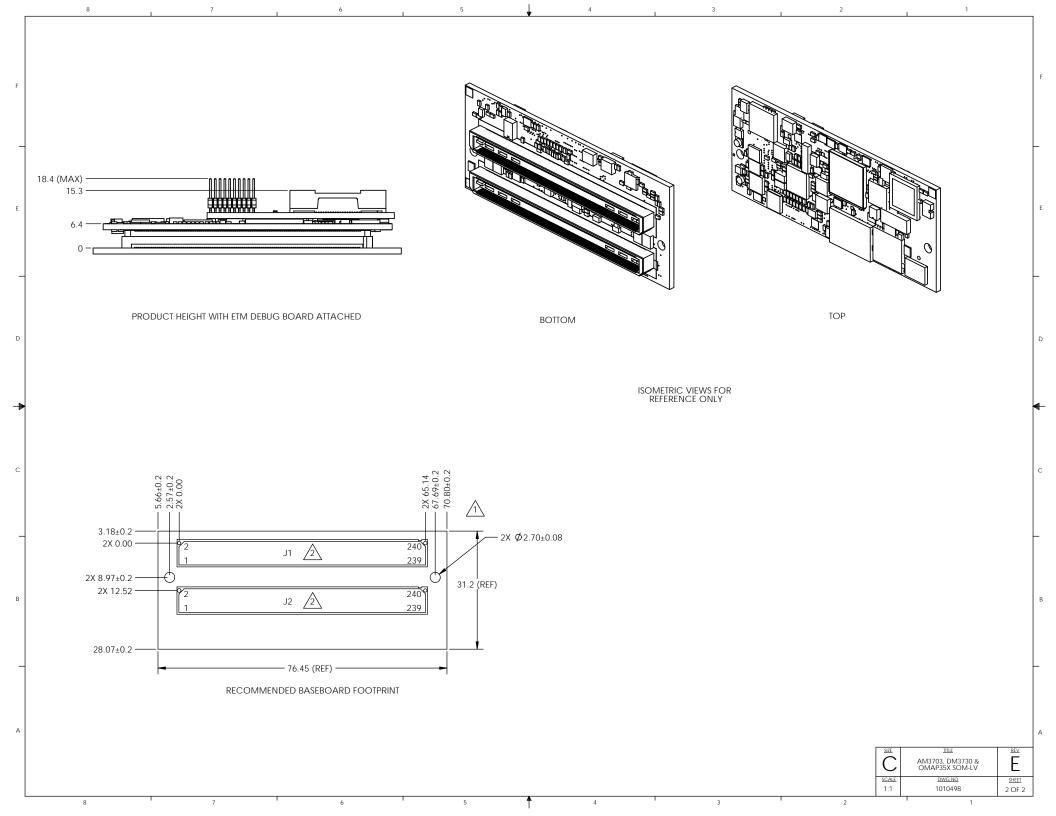

Figure 2.2: OMAP35x SOM-LV Block Diagram

1.

<sup>&</sup>lt;sup>11</sup> http://support.logicpd.com/TechnicalSupport/AskAQuestion.aspx

### 2.3 Mechanical Specification

#### 2.3.1 Interface Connectors

The OMAP35x SOM-LV connects to a PCB baseboard through two 240-pin board-to-board (BTB) socket connectors.

Table 2.1: Baseboard Mating Connectors

| Ref Designator |        | OMAP35x SOM-LV<br>Connector P/N | Mating Connector P/N |

|----------------|--------|---------------------------------|----------------------|

| J1, J2         | Samtec | BTH-120-01-L-D-A                | BSH-120-01-L-D-A     |

### 2.3.2 Wireless Antenna Connectors

The OMAP35x SOM-LV mechanical drawings in Appendix A show the locations of the 802.11b/q/n Ethernet and Bluetooth antenna connectors on the top side of the PCB.

Table 2.2: Antenna PCB Connectors

| Ref Designator | Manufacturer | P/N        |  |

|----------------|--------------|------------|--|

| J3, J4         | Hirose       | U.FL-R-SMT |  |

The table below contains the manufacturer information for the cables and antenna that Logic PD provides in the OMAP35x Development Kit.

Table 2.3: Antennas Included in Development Kit

| Ref Designator | Manufacturer         | P/N                         |  |

|----------------|----------------------|-----------------------------|--|

| Antenna Cable  | Sunridge Corporation | MCBG-RH-54-080-<br>SMAJB281 |  |

| Antenna        | Pulse Engineering    | W1030                       |  |

### 2.3.3 Mounting Specifications

Attach spacers between the OMAP35x SOM-LV and the baseboard to provide additional support when securing the OMAP35x SOM-LV to the baseboard.

Table 2.4: Support Spacers to Secure OMAP35x SOM-LV to Baseboard

| Manufacturer PN |          | Description                    |

|-----------------|----------|--------------------------------|

| Bivar           | 9908-5MM | Nylon screw (#4) spacers, 5 mm |

Securing the OMAP35x SOM-LV to the baseboard requires screws of size 3 or smaller.

Only use flat washers with diameters of 3.8 mm or smaller when securing the OMAP35x SOM-LV to the baseboard. Any other washer type or size may result in cut traces or component and PCB damage leaving the OMAP35x SOM-LV inoperable.

**IMPORTANT NOTE:** Do not apply an excessive amount of torque when securing the OMAP35x SOM-LV to the baseboard. Using more torque than necessary may damage the OMAP35x SOM-LV.

### 2.3.4 OMAP35x SOM-LV Mechanical Drawings

Please see Appendix A for mechanical drawings of the OMAP35x SOM-LV and recommended baseboard footprint layout.

# 3 Electrical Specification

Table 3.1: Absolute Maximum Ratings

| Parameter                     | Symbol       | Rating     | Unit |

|-------------------------------|--------------|------------|------|

| DC 3.3 V Supply Voltage       | 3.3V         | 0.0 to 3.6 | V    |

| DC 5 V Supply Voltage         | 5V           | 0.0 to 7.0 | V    |

| DC Main Battery Input Voltage | MAIN_BATTERY | 0.0 to 4.5 | V    |

| RTC Backup Battery Voltage    | BACKUP_BATT  | 0.0 to 3.3 | V    |

**NOTE:** These stress ratings are only for transient conditions. Operation at or beyond absolute maximum rating conditions may affect reliability and cause permanent damage to the OMAP35x SOM-LV and its components.

**Table 3.2: Recommended Operating Conditions**

| Parameter                        | Min           | Typical               | Max | Unit | Notes  |

|----------------------------------|---------------|-----------------------|-----|------|--------|

| DCM: Bu I IV                     | 2.7*          | 2.2                   | 4.2 | .,   |        |

| DC Main Battery Input Voltage    | (see note 11) | 3.3                   | 4.3 | V    | 11     |

| DC Main Battery Active Current   | _             | 300                   | _   | mA   | 4      |

| DC Main Battery Active Current   | _             | 234                   | _   | mA   | 5      |

| DC Main Battery Active Current   | _             | 162                   | _   | mA   | 6      |

| DC Main Battery Suspend Current  | _             | 102                   | _   | mA   | 7      |

| DC Main Battery Standby Current  | _             | _                     | _   | mA   |        |

| DC 3.3 V Voltage                 | 3.0           | 3.3                   | 3.6 | V    |        |

| DC 3.3 V Active Current          | _             | 118                   | _   | mA   | 4      |

| DC 3.3 V Active Current          | _             | 58                    | _   | mA   | 5      |

| DC 3.3 V Active Current          | _             | 120                   | _   | mA   | 6      |

| DC 3.3 V Suspend Current         | _             | 88                    | _   | mA   | 7      |

| DC 3.3 V Standby Current         | _             | _                     | _   | mA   |        |

| DC 5 V Voltage                   | 4.6           | 4.6                   | 7.0 | V    | 8,9,10 |

| DC RTC Backup Battery Voltage    | 1.8           | 3.2                   | 3.3 | V    |        |

| 802.11b Transmit Power           | +16           | +18                   | +20 | dBm  | 12     |

| 802.11b Receive Sensitivity      | _             | -87                   | -76 | dBm  | 12     |

| 802.11g Transmit Power           | +11           | +13                   | +15 | dBm  | 12     |

| 802.11g Receive Sensitivity      | _             | -73                   | -68 | dBm  | 12     |

| 802.11n Transmit Power           | +10           | +12                   | +14 | dBm  | 12     |

| 802.11n Receive Sensitivity      | _             | -67                   | -64 | dBm  | 12     |

| Commercial Operating Temperature | 0             | 25                    | 70  | °C   |        |

| Extended Operating Temperature   | -20           | _                     | 70  | °C   |        |

| Industrial Operating Temperature | -40           | _                     | 85  | °C   |        |

| Storage Temperature              | -40           | 25                    | 85  | °C   |        |

| Dimensions                       | _             | 31.2 x 76.45<br>x 7.4 | _   | mm   |        |

| Parameter                   | Min         | Typical | Max         | Unit   | Notes |

|-----------------------------|-------------|---------|-------------|--------|-------|

| Weight                      | _           | 17      | _           | Grams  | 2     |

| Connector Insertion/Removal | _           | 50      | _           | Cycles |       |

| Input Signal High Voltage   | 0.65 x VREF | _       | VREF        | V      | 3     |

| Input Signal Low Voltage    | -0.3        | _       | 0.35 x VREF | V      | 3     |

| Output Signal High Voltage  | VREF - 0.2  | _       | VREF        | V      | 3     |

| Output Signal Low Voltage   | GND         | _       | 0.2         | V      |       |

#### **TABLE NOTES:**

- 1. General note: CPU power rails are sequenced on the module.

- 2. May vary depending on OMAP35x SOM-LV configuration.

- 3. VREF represents the peripheral I/O supply reference for the specific CPU voltage rail.

- 4. Full Run [Active], while(1) loop in LogicLoader v2.4.13P1 on a fully-populated OMAP35x SOM-LV. No peripherals attached.

- 5. Full Run [Active], Linux BSP v2.6.32-bsp-2.1 on a fully-populated OMAP35x SOM-LV. No peripherals attached.

- 6. Full Run [Active], Windows CE BSP v2.0.1 on a fully-populated OMAP35x SOM-LV. No peripherals attached.

- 7. Suspend current is measured while running Windows CE BSP v2.0.1 after pushing the S2 button on the SDK2-APP-10 baseboard to enter suspend mode.

- 8. Please see Section 5.6.1.2 for detailed information about 5V usage on the OMAP35x SOM-LV.

- 9. The minimum voltage value of the charging device is:VBATMAX + 2 PMOS drop + 0.22 ohm resistor drop (where VBATMAX is the maximum voltage value of the battery; that is, 4.2V for Li-ion battery)

- 10. High input voltage levels may limit the charging capabilities of the OMAP35x SOM-LV. Please reference Logic PD's *OMAP35x SOM-LV Power Management Application Note* for more information.

- 11. 2.7V is the minimum threshold for the battery at which the device will power OFF. However, the minimum voltage at which the device will power ON is 3.2V ±100mV (if PWRON does not have a switch and is connected to MAIN\_BATTERY) considering battery plug as the device switch on event. If PWRON has a switch then 3.2V is the minimum for the device to power ON.

- 12. Wireless numbers taken from the Murata LBEH19XMMC Module Datasheet (Rev. I). Logic PD is working to verify these numbers using the OMAP35x SOM-LV.

## 4 Peripheral Specification

#### 4.1 Clocks

The OMAP35x processor requires an oscillator and crystal to enable proper internal timing. A 26.000 MHz oscillator is used to generate many of the processor's internal clocks via a series of Phase Lock Loops (PLLs) and signal dividers. To generate the core CPU clock, the 26.000 MHz signal is run through a Digital PLL controlled by the PRCM registers. Divisors are used to divide down the internal bus frequency to set the LCD, memory controller, camera interface, etc.

**IMPORTANT NOTE:** Please see TI's *OMAP35x TRM* for additional information about processor clocking.

The second required crystal runs at 32.768 kHz and is connected directly to the TPS65950. The 32.768 kHz clock is used for PMIC and CPU start up and as a reference clock for the real time clock (RTC) module.

The CPU's microcontroller core clock speed is initialized by software on the OMAP35x SOM-LV. The SDRAM bus speed is set at 166 MHz in LogicLoader. Other clock speeds, such as core speed and specific serial baud rates, can be supported and modified in software for specific user applications.

The OMAP SOM-LV provides an external bus clock, uP\_BUS\_CLK. This clock is driven by the GPMC CLK pin.

| OMAP35x Microcontroller<br>Signal Name | OMAP35x SOM-LV<br>Net Name | Default Software Value in LogicLoader |

|----------------------------------------|----------------------------|---------------------------------------|

| CORE                                   | N/A                        | Up to 600 MHz                         |

| SDRC_CLK                               | SDRC_CLK                   | 166 MHz                               |

| GPMC_CLK                               | uP_BUS_CLK                 | Not configured                        |

Table 4.1: Processor Clock Specifications

### 4.2 Memory

### 4.2.1 Package-on-Package Memory (Mobile DDR and NAND)

The OMAP35x processor uses Package-on-Package (PoP) technology to stack BGA memory devices on top of the CPU BGA. The processor uses a 32-bit memory bus to interface to mobile DDR (mDDR) SDRAM and a 16-bit memory bus to interface to NAND. The PoP devices can be ordered with the following density options:

- 128 MB mDDR and 256 MB NAND

- 256 MB mDDR and 512 MB NAND

Logic PD's default memory configuration on the OMAP35x SOM-LV included in the OMAP35x Development Kit is specified as 128 MB mDDR and 256 MB NAND.

#### 4.2.2 NOR Flash

The OMAP35x SOM-LV uses the 16-bit GPMC memory bus to interface to a single NOR flash memory chip. The onboard SOM-LV NOR flash memory can be configured as 0, 8, 16, 32, or 64 MB to meet the user's flash requirements and cost constraints. Logic PD's default flash configuration is 16 MB on the OMAP35x SOM-LV included in the standard OMAP35x Development Kit. Because flash is one of the most expensive components on the OMAP35x SOM-LV, it is important to contact Logic PD when determining the necessary flash size for final product configuration. NAND flash is a lower cost alternative that should be considered for final product configuration.

It is possible to expand the system's non-volatile storage capability by adding external flash ICs, SD memory, CompactFlash, or NAND flash. Please <u>contact Logic PD</u> for other possible peripheral designs.

#### 4.2.3 PC Card Interface

The OMAP35x CPU does not directly support PCMCIA or CompactFlash slots. The OMAP35x SOM-LV uses internal logic to provide the necessary signals for the CompactFlash interface, creating support for a single external memory-mode only CompactFlash card. The OMAP35x Development Kit reference design includes a hot-swappable CompactFlash connector. Additional CompactFlash slots can be added using the GPMC bus. For more information on implementing additional slots, contact Logic PD.

### 4.2.3.1 Example CompactFlash Timing

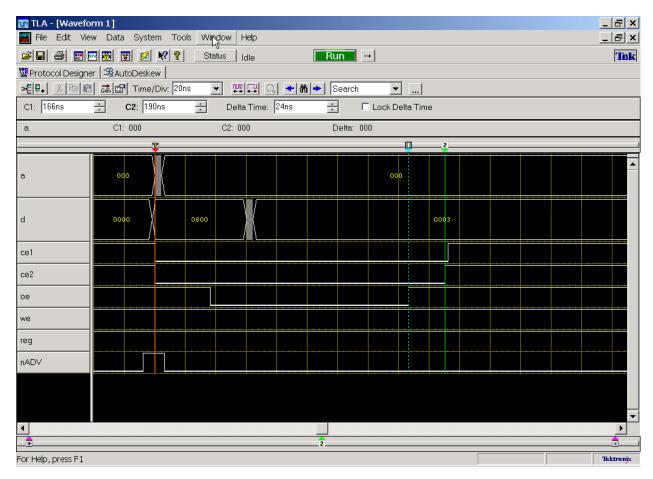

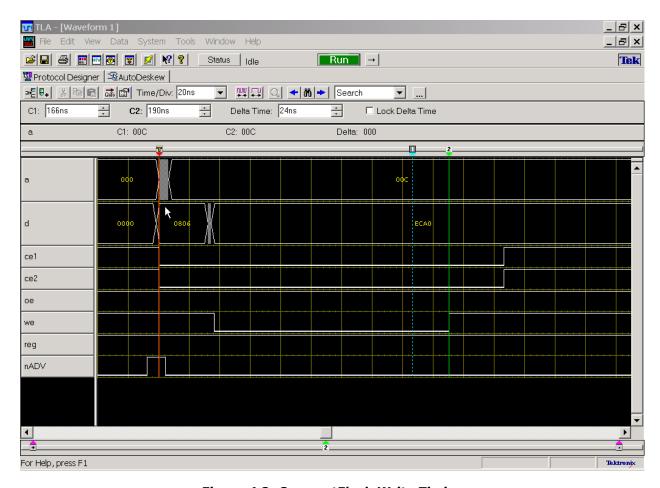

On the OMAP35x SOM-LV, the CompactFlash interface (nCS3 of the GPMC bus) is set up with the following register settings:

```

0x6e00_00f0 0x0000_1210

0x6e00_00f4 0x0013_1000

0x6e00_00f8 0x001F_1F01

0x6e00_00fC 0x1003_0E03

0x6e00_0100 0x010F_1411

0x6e00_0104 0x8003_0600

0x6e00_0108 0x0000 0F58

```

These settings yield the following timing diagrams, which conform to the *CompactFlash Specification Revision 3.0*.

Figure 4.1: CompactFlash Read Timing

Figure 4.2: CompactFlash Write Timing

### 4.3 **10/100 Ethernet PHY**

The OMAP35x SOM-LV uses an SMSC LAN9221 Ethernet MAC+PHY to provide an easy-to-use networking interface. The four analog PHY interface signals (transmit/receive) each require an external impedance matching circuit to operate properly. Logic PD provides an example impedance matching circuit schematic in the *OMAP35x Development Kit Baseboard Schematic*. Note that the OMAP35x Development Kit Baseboard uses an Ethernet socket with integrated magnetics. Also, please note the TX+/- and RX+/- pairs must be routed as differential pairs on the baseboard PCB.

### 4.4 802.11 Wireless Ethernet

The OMAP35x SOM-LV uses a Murata LBEH19XMMC 802.11b/g/n + Bluetooth 2.1 Wireless IC to provide an easy-to-use wireless networking interface. The LBEH19XMMC is connected to the OMAP35x processor through SDIO3 and the connector is located on the PCB at reference designator J4.

**NOTE:** The Bluetooth interface on the LBEH19XMMC is not used. Please see Section 4.5 for Bluetooth on the OMAP35x SOM-LV.

#### 4.5 Bluetooth

The OMAP35x SOM-LV uses a TI HPABT6300 BlueLink to provide a Bluetooth interface. The HPABT6300 is connected to the OMAP35x processor through McSPI1 and PCM. The connector is located on the PCB at reference designator J3.

### 4.6 Audio Codec

The OMAP35x processor has multiple Multi-channel Buffered Serial Port (McBSP) interfaces that support PCM and I2S formats. Both PCM and I2S serial paths drive the built-in TPS65950 audio codec. From the TPS65950, the outputs are CODEC\_OUTL and CODEC\_OUTR; these signals are available from the expansion connectors.

The codec in the TPS65950 performs up to full-duplex codec functions and supports variable sample rates from 8–96k samples per second. See the "Audio" chapter in TI's TPS65950 OMAP Power Management and System Companion Device TRM for more information.

**NOTE:** The OMAP35x SOM-LV also offers alternate serial interfaces for other codec devices. If you are looking for a different codec option, Logic PD has previously interfaced different high-performance audio codecs into other SOMs. <u>Contact Logic PD</u> for assistance in selecting an appropriate audio codec for your application.

### 4.7 Display Interface

The OMAP35x processor has a built-in LCD controller supporting STN, color STN, and TFT panels at a resolution of up to XGA 1024 x 768 x 24-bit color. See TI's *OMAP35x TRM* for further information on the integrated LCD controller. The signals from the OMAP35x LCD controller are organized by bit and color and can be interfaced through the expansion connectors. Logic PD has written drivers for panels of different types and sizes. Please contact Logic PD before selecting a panel for your application.

**IMPORTANT NOTE:** Using the internal graphics controller will affect processor performance. Selecting display resolutions and color bits per pixel will vary processor busload.

### 4.8 Serial Interfaces

The OMAP35x SOM-LV comes with the following serial channels: UARTA, UARTB, UARTC, SPI, and two I2C ports. If additional serial channels are required, please contact Logic PD for reference designs. Please see TI's OMAP35x TRM for further information regarding serial communications.

### 4.8.1 UARTA

UARTA has been configured as the main OMAP35x SOM-LV serial port based on the processor UART1. It is an asynchronous 16C750-compatible UART. This UART provides a high-speed serial interface that uses 64 byte First In / First Out (FIFO) and is capable of sending and receiving serial data simultaneously. The signals from the OMAP35x SOM-LV are 1.8V Transistor-Transistor Logic (TTL) level signals, not RS232 level signals. The end-product design must provide an external RS232 transceiver for RS232 applications. Logic PD has provided an example reference design with the *OMAP35x Development Kit Baseboard*

Schematic document. When choosing an RS232 transceiver, the designer should keep cost, availability, ESD protection, and data rates in mind.

The UARTA baud rate is set to a default 115.2 Kbits/sec, though it supports most common serial baud rates.

### 4.8.2 UARTB

Serial Port UARTB (processor UART3) is an asynchronous 16C750-compatible UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the OMAP35x SOM-LV are TTL level signals, not RS232 level signals. The UARTB baud rate can also be set to most common serial baud rates.

#### 4.8.3 UARTC

Serial port UARTC (processor UART2) is an asynchronous 16C750-compatible UART. This UART is a high-speed serial interface that uses FIFO and is capable of sending and receiving serial data simultaneously. The signals from the OMAP35x SOM-LV are TTL level signals, not RS232 level signals. The UARTC baud rate can also be set to most common serial baud rates.

#### 4.8.4 McSPI

The OMAP35x SOM-LV provides an external SPI port with multiple chip selects.

#### 4.8.5 I2C

The OMAP35x SOM-LV supports two dedicated external I2C ports. The clock and data signals for both ports have 4.7K pull-up resistors to their respective power rails on the SOM. Please see TI's OMAP35x TRM for further information.

#### 4.8.5.1 Reserved I2C Addresses

The OMAP35x SOM-LV contains a product ID chip that connects to the I2C bus. Logic PD software uses this product ID chip to determine hardware version information. As a result, the 7-bit I2C addresses listed below are used by the product ID chip and must be avoided in custom designs:

- **101 1000**

- **101 1001**

- **101 1010**

- **101 1011**

- **101 1100**

- **101 1101**

### 4.9 USB Interface

The OMAP35x SOM-LV supports three USB 2.0 high-speed host ports and one USB 2.0 On-the-Go (OTG) port, which can function as a host or device/client. In order to for the port to operate as a host, a proper adapter cable must be used; Logic PD recommends one similar to

the USB adapter cable by  $\underline{\text{Digi-Key}^{12}}$  (part number 10-00003-ND). All ports can operate at up to 480 Mbit/sec. The processor has the USB controller internal to the OMAP for the OTG port; an external PHY built into the TPS65950 supports the OTG port.

The OMAP35x SOM-LV also has an external USB transceiver to support high-speed host. The external transceiver is an SMSC USB3320 that is connected through the USB2 ULPI interface of the OMAP35x microcontroller. The output of the USB3320 is routed to an SMSC USB2513 USB high-speed hub. The USB2513 is used to generate the three high-speed USB host ports that go off-board: USB2, USB4, and USB5. For more information on using both the USB host and OTG interfaces, please see TI's OMAP35x TRM.

**IMPORTANT NOTE:** In order to correctly implement USB on the OMAP35x SOM-LV, additional impedance matching circuitry may be required on the USBx\_D+ and USBx\_D- signals before they can be used. USB 2.0 requirements specify the signals must be routed as differential pairs with 90 ohm differential impedance. Refer to the *USB 2.0 Specification* for detailed information.

### 4.10 ADC/Touch Interface

The OMAP35x SOM-LV uses TI's TSC2004 Touch Screen Controller (TSC). The controller includes a 12-bit analog-to-digital converter (ADC). This TSC is used to support standard 4-wire resistive touch panels and one auxiliary A/D signal. The device is connected to the CPU by the OMAP I2C3 interface. Please see TI's TSC2004 Datasheet for more information.

### 4.11 General Purpose I/O

Logic PD designed the OMAP35x SOM-LV to be flexible and provide multiple options for analog and digital GPIO. There are numerous digital GPIO pins on the OMAP35X SOM-LV that interface to the OMAP35x processor and TPS65950 PMIC; please see Section 7 for more information. If certain peripherals are not desired, such as the LCD controller, chip selects, IRQs, or UARTs, more GPIO pins become available.

**DESIGN NOTE:** Due to buffer strength, an external serial resistor must be connected to the BGA balls where GPIO\_120 through GPIO\_129 are muxed with MMC signals. See "Section 24.2" in TI's *OMAP35x TRM* for additional information.

### 4.12 Onboard Logic Interfaces

The onboard logic interfaces are used to create additional functionality on the OMAP35x SOM-LV with the support of a few discrete logic components.

### 4.13 Expansion/Feature Options

The OMAP35x SOM-LV was designed for expansion and a variable feature set, providing all the necessary control signals and bus signals to expand the user's design. Some of these signals are buffered and brought out to the expansion connectors. It is possible for a user to expand the OMAP35x SOM-LV's functionality even further by adding host bus or ISA bus devices. Some features that are implemented on the OMAP35x processors but are not discussed herein

include: RTC, pulse width modulation (PWM), Secure Digital, MMC cards, SDIO cards, graphics accelerator, DSP codecs, Image Processing Unit, 1-wire interface, and the debug module. See TI's OMAP35x TRM and Logic PD's OMAP35X SOM-LV Schematic for more details.

Logic PD has experience implementing additional options, including other audio codecs, Ethernet ICs, co-processors, and components on SOMs. Please contact Logic PD for potential reference designs before selecting your peripherals.

**DESIGN NOTE:** The OMAP General Purpose Memory Controller (GPMC) bus is used by several peripherals on the OMAP35x SOM-LV. It is recommended that only one external device be connected to the GPMC bus. If more than one device is required, a buffer should be used.

**DESIGN NOTE:** Due to buffer strength, an external serial resistor must be connected to the BGA balls corresponding to any MMC/SD1 signal or alternate function on those same BGA balls. See "Section 24.2" in TI's *OMAP35x TRM* for additional information.

## 5 System Integration

### 5.1 Configuration

The OMAP35x SOM-LV was designed to meet multiple applications for users with specific design and budget requirements. As a result, this OMAP35x SOM-LV supports a variety of embedded operating systems and supports the following hardware configurations:

- Flexible memory footprint: 128 or 256 MB mobile DDR SDRAM

- Flexible NOR flash footprint: 0, 8, 16, or 32 MB NOR flash

- Flexible NAND flash footprint: 0, 256, or 512 MB

- Optional SMSC LAN9221 10/100 Ethernet PHY

- Optional Murata LBEH19XMMC 802.11b/g/n

- Optional TI BRF6300 Bluetooth

Please contact Logic PD for additional hardware configurations to meet your application needs.

### 5.2 Resets

The OMAP35x SOM-LV has a reset input (MSTR\_nRST) and a reset output (RESET\_nOUT/SYS\_nRESWARM). External devices use MSTR\_nRST to assert reset to the product. The OMAP35x SOM-LV uses RESET\_nOUT to indicate to other devices that the SOM is in reset.

#### 5.2.1 Master Reset (MSTR\_nRST)—Reset Input

Logic PD suggests that custom designs implementing the OMAP35x SOM-LV use the MSTR\_nRST signal as the "pin-hole" reset used in commercial embedded systems. The MSTR\_nRST triggers a power-on-reset event to the OMAP35x processor and resets the entire CPU.

**IMPORTANT NOTE:** The MSTR\_nRST does not reset the TPS65950 PMIC; the PMIC is only reset by removing power from the SOM. Any custom reset circuit design should guard the assertion of the reset lines during a low power state so as to prevent power-up in a low or bad power condition. (Powering up in a low or bad power condition will cause data corruption and, possibly, temporary system lockup). See Section 5.6 for further details. Either one of the following two conditions will cause a system-wide reset: power on the MSTR\_nRST signal or a low pulse on the MSTR\_nRST signal.

#### Low Pulse on MSTR\_nRST Signal:

A low pulse on the MSTR\_nRST signal, asserted by an external source (for example, the reset button on the custom design application) will bring MSTR\_nRST low until the assertion source is de-asserted. There is no delay beyond the de-assertion of the external MSTR\_nRST signal source, so the custom design must ensure that the assertion time is sufficient for all related peripherals.

Logic PD suggests that de-bouncing be used to generate a clean, one-shot reset signal for any external assertion source that triggers the MSTR\_nRST signal, analog or digital.

### 5.2.2 OMAP35x SOM-LV Reset (RESET\_nOUT/SYS\_nRESWARM)—Reset output

All hardware peripherals should connect their hardware-reset pin to the RESET\_nOUT (SYS\_nRESWARM) signal on the expansion connector. Internally, all OMAP35x SOM-LV peripheral hardware reset pins are connected to the RESET\_nOUT net.

If the output of the onboard voltage-monitoring circuit is asserted (active low), the user can expect to lose information stored in RAM. The data loss occurs because the CPU is reset to its reset defaults.

### 5.3 Interrupts

The OMAP35x processor incorporates the ARM Cortex-A8 interrupt controller, which provides many inter-system interrupt sources and destinations. Most external GPIO signals can also be configured as interrupt inputs by configuring their pin control registers. Logic PD BSPs set up and process all onboard system and external OMAP35X SOM-LV interrupt sources. Refer to TI's *OMAP35x TRM* for further information on using interrupts.

### **5.4 JTAG Debugger Interface**

The JTAG connection on the OMAP35x SOM-LV allows recovery of corrupted flash memory, real-time application debug, and DSP development. There are several third-party JTAG debuggers available for TI microcontrollers. The following signals make up the JTAG interface to the OMAP35x processor: TDI, TMS, TCK, TDO, nTRST, RTCK, EMU0, EMU1, and MSTR\_nRST (MSTR\_nRST is only required for some JTAG tools; see the JTAG tool documentation for exact pinout). These signals should interface directly to a 20-pin 0.1" through-hole connector, as shown on the *OMAP35x Development Kit Baseboard Schematic*.

**IMPORTANT NOTE:** When laying out the 20-pin connector, realize that it may not be numbered as a standard 20-pin 0.1" insulation displacement connector (IDC) through-hole connector. See the OMAP35x Development Kit reference design for further details. Each JTAG tool vendor may define the 20-pin IDC connector pin-out differently.

### 5.5 ETM Adapter Interface

The Embedded Trace Macrocell (ETM) interface signals are available through connector J5 on the OMAP35x SOM-LV. Logic PD developed an adapter board, included with the OMAP35x Development Kit, that converts the available signals on J5 to the standard Mictor connector interface used by most common third-party ETM tool providers. The connector supports ETM D[15:0], ETM CLK, ETM CTL, and the JTAG signals listed in Section 5.4.

**IMPORTANT NOTE:** The ETM interface will not operate at fastest speed due to multiplexed signals.

### 5.6 Power Management

### 5.6.1 System Power Supplies

In order to ensure a flexible design, the OMAP35x SOM-LV has the following power areas: MAIN\_BATTERY, 5V, 3.3V, BACKUP\_BATT. All power areas are inputs to the OMAP35x SOM-LV. The module also provides reference voltages to specific peripheral areas. Reference voltages are named VREF\_xxxx on the expansion connectors. They are outputs from the OMAP35x SOM-LV and should only be used as reference voltage inputs to level shifting devices on baseboard designs.

**IMPORTANT NOTE:** If USB1\_VBUS is powered externally it will power the SOM, even if MAIN\_BATTERY is disconnected. Additionally, if U24 is populated, USB1\_VBUS can charge MAIN\_BATTERY. This functionality can be controlled by software. Please refer to the *TPS65950 TRM* for more information.

#### 5.6.1.1 MAIN\_BATTERY

The MAIN\_BATTERY input is the main source of power for the OMAP35x SOM-LV. This input expects a voltage within typical single lithium-ion battery limits which generally operate from 2.8 V to 4.2 V. If a lithium-ion battery is not used as the main power source, it is recommended to supply a fixed 3.3 V supply. The TPS65950 power management controller takes the MAIN\_BATTERY rail input and creates all onboard voltages. If the design is required to maintain RAM contents in a critical power situation (e.g., low battery, loss of power), the MAIN\_BATTERY supply should be maintained above the minimum level at all costs (see Section 2). Logic PD suggests using standby mode to prepare the system for a critical power condition. In this way, the SDRAM is placed into self-refresh and the processor is placed into the standby state. (Please note the description of standby mode in Section 5.6.3.3 below.) The MAIN\_BATTERY supply must stay within the acceptable levels specified in Section 2 unless experiencing power down or critical power conditions.

#### 5.6.1.2 5V

The 5V input is not required for product operation. The 5V input is only used when the charge path components are populated on the OMAP35x SOM-LV. These optional charge path circuits allow in-system charging of a single cell lithium-ion battery source when a 5V power is applied to the 5V supply. Some designs will require a separate battery charging circuit on the baseboard to charge the main battery source. Charge current is limited to 1 Amp.

### 5.6.1.3 3.3V

The 3.3V rail is used to power a few legacy interfaces on the OMAP35x SOM-LV that require 3.3V. The baseboard should provide 3.3V to the OMAP35x SOM-LV when 10/100 Ethernet, USB host, or the ETM interface is required on the final product. Typically this can be implemented as a low dropout (LDO) or switching regulator connected to the MAIN\_BATTERY power source on the baseboard. The 3.3V supply must stay within the acceptable levels specified in Section 2 unless experiencing power down or critical power conditions. Under critical power conditions, Logic PD suggests notifying the system through the assertion of a standby sequence first and then powering off this supply.

**IMPORTANT NOTE:** The 3.3V rail is required when Ethernet or USB are populated to prevent these devices from pulling the GPMC bus signals low or causing damage due to back power.

Ethernet and USB are populated on all standard configuration OMAP35x SOM-LVs; if a standard OMAP35x SOM-LV is used to test custom baseboard designs, there must be a method to apply 3.3V to the OMAP35x SOM-LV. This 3.3V circuitry can be removed after development if the production OMAP35x SOM-LV does not contain Ethernet or USB.

### **5.6.1.4 BACKUP\_BATT**

The BACKUP\_BATT power rail is used to power the onboard TPS65950 PMIC, power management state machine, and RTC circuit when MAIN\_BATTERY is not present. Always power this rail to maintain the clock and power state of the product. A lithium-ion coin cell typically supplies power to this rail. The TPS65950 PMIC overrides this input when MAIN\_BATTERY is applied.

### 5.6.2 System Power Management

Good power management design is important in any system development and embedded system design is no exception. In embedded system design, power management is typically one of the most complicated areas due to the dramatic effect it has on product cost, performance, usability, and overall customer satisfaction. Many factors affect a power-efficient hardware design: power supply selection (efficiency), clocking design, IC and component selection, etc. The OMAP35x SOM-LV was designed with these aspects in mind while also providing maximum flexibility in software and system integration.

On the OMAP35x SOM-LV there are many different software configurations that drastically affect power consumption: microcontroller core clock frequency, bus clock frequency, peripheral clocks, bus modes, power management states; peripheral power states and modes; product user scenarios; interrupt handling; and display settings (resolution, backlight, refresh, bits per pixel, etc). These settings are typically initialized in the startup software routines and may be modified later in the operating system and application software. Information on these items can be found in the appropriate documents such as the *LogicLoader v2.4 User Manual* or the specific BSP manual.

#### 5.6.3 Microcontroller

The OMAP35x processor's power management scheme was designed for the cellular handset market, so naturally the static and dynamic power consumption has very flexible controls allowing designers to tweak the processor to minimize end-product power consumption. Logic PD software BSPs take advantage of dynamic power switching (DPS) and SmartReflex adaptive voltage control (AVC) to maximize power savings.

#### 5.6.3.1 Run State

Run is the normal operating state for the OMAP35x SOM-LV in which oscillator outputs and all clocks are hardware enabled. The OMAP35x SOM-LV can enter run mode from any state. A standby-to-run transition occurs on any valid wakeup event, such as the assertion or any enabled interrupt signal. All required power supplies are active in this state. Please see TI's OMAP35xTRM for further information.

### 5.6.3.2 Suspend State

Suspend is the hardware power-down state for the OMAP35x SOM-LV, allowing for lower power consumption. The suspend state is designed to reduce power consumption while the OMAP35x SOM-LV is waiting for an event, such as a keyboard input. In Logic PD BSPs, the suspend state is entered by asserting the nSUSPEND signal or through software commands. All power supplies remain active and system context is retained. An internal or external wakeup event can cause the processor to transition back to run mode. Please see TI's OMAP35x TRM for further information.

#### 5.6.3.3 Standby State

Standby is the lowest power state for the OMAP35x SOM-LV. This state is entered in Logic PD BSPs by asserting the nSTANDBY signal or through software commands. The OMAP35x processor is put into the lowest power state and all clocks are stopped. The MAIN\_BATTERY power rail should be maintained if the low-power DDR SDRAM contents wish to be retained. Internal or external wakeup events can cause a return to the run state.

### 5.7 ESD Considerations

The OMAP35x SOM-LV was designed to interface to a customer's peripheral board, while remaining low cost and adaptable to many different applications. The OMAP35x SOM-LV does not provide any onboard ESD protection circuitry—this must be provided by the product in which it is used. Logic PD has extensive experience in designing products with ESD requirements. Please <a href="contact\_Logic PD">contact\_Logic PD</a> if you need any assistance in ESD design considerations.

# 6 Memory & I/O Mapping

On the OMAP35x microcontroller, all address mapping for the GPMC chip select signals is listed below. Mapped chip select signals for the processor are available as outputs from the microcontroller and are assigned as described in Table 6.1 below.

| Chip Select | Device/Feature                       | Notes                                                                               |

|-------------|--------------------------------------|-------------------------------------------------------------------------------------|

| nCS0        | POP NAND / boot NOR                  | Boot chip select for POP NAND device or external NOR when POP does not include NAND |

| nCS1        | 10/100 Ethernet                      | SMSC LAN9221                                                                        |

| nCS2        | ON-/OFF-board NOR                    | Micron Parallel NOR Flash Embedded Memory                                           |

| nCS3        | External Memory Mode<br>CompactFlash |                                                                                     |

| nCS4        | External nCS_A                       | Available for use by an off-board external device                                   |

| nCS5        | External nCS_B                       | Available for use by an off-board external device                                   |

Table 6.1: Chip Select Signals

**NOTE:** Memory addresses for chip selects on the OMAP35x SOM-LV are configurable by software; therefore, precise address locations cannot be provided. Please consult the *LogicLoader v2.4 User Manual* and the *OMAP35x SOM-LV LogicLoader User Manual Addendum* for memory map information.

## 7 Pin Descriptions and Functions

**IMPORTANT NOTE:** The following pin descriptions and states are provided for the default pin usage. Many of the signals defined in the tables below can be configured as input or outputs—most GPIOs on the OMAP35x processor can be configured as either inputs or outputs—and have different functions. It is critical to review all signals in the final design (both electrical and software) to verify the necessary configuration (external pull-ups/pull-downs).

**IMPORTANT NOTE:** Please pay attention to the reference voltage used to power each signal in the table below, especially when used as a GPIO. Not all power rails coming out of the TPS65950 PMIC are turned on by default and may need to be enabled by software. Reference voltages for OMAP35x processor signals can be found in TI's *OMAP3530/25 Applications Processor Datasheet*.

**NOTE:** When two signal names are provided, the signals in parentheses are the net names specific to OMAP35x SOM-LV; the non-parenthetical names are the signal names that are general to the SOM-LV form factor.

### 7.1 J1 Connector 240-Pin Descriptions

| J1<br>Pin# | Signal Name | BGA Ball #         | Processor Signal | I/O | Voltage | Description                              |

|------------|-------------|--------------------|------------------|-----|---------|------------------------------------------|

| J1.1       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.2       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.3       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.4       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.5       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.6       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.7       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.8       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.9       | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.10      | RFU         | _                  | _                | I/O | NA      | Reserved for future use. Do not connect. |

| J1.11      | DGND        | (See<br>Schematic) | (See Schematic)  | I   | GND     | Ground. Connect to digital ground.       |

| J1.12      | DGND        | (See<br>Schematic) | (See Schematic)  | I   | GND     | Ground. Connect to digital ground.       |

| J1<br>Pin# | Signal Name | BGA Ball #         | Processor Signal                                     | I/O | Voltage                    | Description                                                                                                                                                                                                                                              |

|------------|-------------|--------------------|------------------------------------------------------|-----|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1.13      | uP_nWAKEUP  | A11(PMIC)          | PWRON(PMIC)                                          | I   | Max 4.3V<br>(MAIN_BATTERY) | Active low. Software can use this signal as an interrupt to transition to RUN state from lower power states. Software is required for proper operation. This signal has a 4.75K pull-up.                                                                 |

| J1.14      | ETHER_TX+   | _                  | _                                                    | 0   | 3.3V                       | This output pair drives 10/100 Mb/s data to the transmit lines. Route as differential pair with ETHER_TX Requires external magnetics. See example LV-Baseboard design for reference components.                                                          |