# Migration Guide for i.MX31, i.MX27, and OMAP35x SOM-LVs

**Application Note 375**

Logic // Embedded Product Solutions Published: October 2008

## **Abstract**

This Application Note assists customers who want to design a custom baseboard that can support the i.MX31, i.MX27, and OMAP35x SOM-LV modules or update their existing baseboard to accommodate a different processor-based SOM-LV module. This document details the differences in the connector pin outs and feature sets between the three SOM-LV modules.

This document contains valuable proprietary and confidential information and the attached file contains source code, ideas, and techniques that are owned by Logic Product Development Company (collectively "Logic's Proprietary Information"). Logic's Proprietary Information may not be used by or disclosed to any third party except under written license from Logic Product Development Company.

Logic Product Development Company makes no representation or warranties of any nature or kind regarding Logic's Proprietary Information or any products offered by Logic Product Development Company. Logic's Proprietary Information is disclosed herein pursuant and subject to the terms and conditions of a duly executed license or agreement to purchase or lease equipment. The only warranties made by Logic Product Development Company, if any, with respect to any products described in this document are set forth in such license or agreement. Logic Product Development Company shall have no liability of any kind, express or implied, arising out of the use of the Information in this document, including direct, indirect, special or consequential damages.

Logic Product Development Company may have patents, patent applications, trademarks, copyrights, trade secrets, or other intellectual property rights pertaining to Logic's Proprietary Information and products described in this document (collectively "Logic's Intellectual Property"). Except as expressly provided in any written license or agreement from Logic Product Development Company, this document and the information contained therein does not create any license to Logic's Intellectual Property.

The Information contained herein is subject to change without notice. Revisions may be issued regarding changes and/or additions.

© Copyright 2008, Logic Product Development Company. All Rights Reserved.

#### **REVISION HISTORY**

| REV | EDITOR       | DESCRIPTION     | APPROVAL | DATE     |

|-----|--------------|-----------------|----------|----------|

| 1   | Brad Brown   | Internal draft  | BB       | 06/27/08 |

| Α   | Jed Anderson | Initial release | BB       | 10/08/08 |

## **Table of Contents**

| 1  |          | ction                                 |    |

|----|----------|---------------------------------------|----|

|    |          | pe of Document                        |    |

| 2  |          | 1ces                                  |    |

|    | 2.1 Sup  | porting Documents                     | 1  |

|    | 2.2 Acr  | onyms                                 | 2  |

| 3  | Genera   | ll Features Overview                  | 3  |

| ,  | 3.1 Me   | chanical Specifications               | 4  |

| 4  | Pin Co   | mparison                              | 5  |

| 5  | PMIC I   | nformation                            | 5  |

| 6  | Detaile  | d Interface Descriptions              | 5  |

|    | 6.1 Pov  | ver/Reset/Clock/PWM Control Signals   | 6  |

|    |          | mory Interfaces                       | 7  |

|    | 6.2.1    | Static Memory Bus Interface           |    |

|    | 6.2.2    | ATA Interface                         |    |

|    | 6.3 Rer  | movable Media Interfaces              |    |

|    | 6.3.1    | PCMCIA/CF Card Interface              |    |

|    | 6.3.2    | MMC/SD Card Interface                 |    |

|    | 6.3.3    | SIM Card Interface                    |    |

|    | 6.4 Cor  | mmunication and Control Interfaces    |    |

|    | 6.4.1    | 1-Wire                                |    |

|    | 6.4.2    | UART Interfaces                       |    |

|    | 6.4.3    | I2S/AC97/PCM                          |    |

|    | 6.4.4    | SPI Interfaces                        |    |

|    | 6.4.5    | USB Interfaces                        |    |

|    | 6.4.6    | Ethernet                              |    |

|    | 6.4.7    | IRQ Routing                           |    |

|    | 6.4.8    | Keypad                                |    |

|    | 6.4.9    | Touch Screen                          |    |

|    |          | CODEC Line-In/Out                     |    |

|    |          | I2C Interfaces                        |    |

|    |          | ADC Interface                         |    |

|    |          | Control Signals and GPIO Signals      |    |

|    | 6.5 Gra  | phic Interfaces                       | 32 |

|    |          | Camera Sensor Interface               |    |

|    |          | LCD Interface                         |    |

|    |          | TV Display Interface                  |    |

|    |          | M/JTAG Interface                      |    |

| 7  |          | ary                                   |    |

|    |          | A: SOM-LV Baseboard Footprint Drawing |    |

|    |          | 3: J1 Connector Pin Comparison        |    |

| Αr | pendix ( | C: J2 Connector Pin Comparison        | 53 |

## 1 Introduction

Logic's System on Modules (SOMs) simplify development and provide the ability to easily upgrade to next generation hardware and software. The SOM-LV is a low-voltage module based on Freescale's i.MX and Texas Instruments' OMAP™ processors. This document will explain indepth differences between the i.MX31, i.MX27, and the OMAP35x SOM-LVs to help in designing a custom baseboard that can accommodate all three modules.

Logic publishes an *Embedded Products Parametric Table* for a high-level description of the feature set available for every SOM we offer. Follow the link below to download a PDF of the Parametric Table.

■ Embedded Products Parametric Table

## 1.1 Scope of Document

Though this document addresses the differences between the modules it is not intended to be all-inclusive. System designers should review the sets of schematics and any other applicable supporting documents for the i.MX31, i.MX27, and the OMAP35x SOM-LV modules before designing a baseboard that can utilize more than one of these products.

**IMPORTANT NOTE:** If there is ever a discrepancy between information within this document and the corresponding schematics, the schematics hold precedence.

## 2 References

## 2.1 Supporting Documents

Listed below are the links to the most current schematics for the i.MX31, i.MX27, and the OMAP35x SOM-LVs. Product registration is required to gain access to these documents. If you do not currently have a registered product, please contact your sales representative for access.

- i.MX31 SOM-LV Schematics

- i.MX27 SOM-LV Schematics

- OMAP35x SOM-LV Schematics

The Zoom Development Kits based on the i.MX31, i.MX27, and OMAP35x SOM-LVs all use the same LV baseboard (SDK2-APP-10). 1

Table 2.1 lists the supporting documents that were used in the creation of this Application Note.

\_

<sup>&</sup>lt;sup>1</sup> The Zoom OMAP35x Development Kit uses a modified baseboard that has resistor R13 removed in order for the included 4.3" WQVGA LCD to work properly.

Table 2.1: Supporting Documents

| Logic PN        | Rev     | Description                                                |

|-----------------|---------|------------------------------------------------------------|

| 1005441         | А       | LV Baseboard (SDK2-APP-10) Schematic                       |

| 1004734         | 11      | i.MX31 SOM-LV Schematics                                   |

| 1009880         | Α       | i.MX27 SOM-LV Schematics                                   |

| 1009917         | Α       | OMAP35x SOM-LV Schematics                                  |

| 1009954         | Α       | OMAP35x SOM-LV Hardware Specification                      |

| 1005992         | Е       | i.MX31 SOM-LV Hardware Specification                       |

| 1007859         | 2       | i.MX27 SOM-LV Hardware Specification                       |

| 70000161        | Α       | Interfacing LCDs to Logic's SDK Board AN 161               |

| TI Literature # | Version | Description                                                |

| SPRS505         | -       | OMAP3515/03 Applications Processor Datasheet               |

| SPRUF98A        | Α       | OMAP35x Multimedia Device Silicon Revision 2.0 and 2.1 TRM |

|                 |         | TPS65950 Integrated Power                                  |

| SWCS019K        | K       | Management/Audio Codec Silicon Revision 3.1 Data Manual    |

|                 |         | TPS65950 OMAP Power Management                             |

| SWCU026P        | Р       | and System Companion Device Silicon Revision 3.1 TRM       |

| Freescale Doc#  | Rev     | Description                                                |

| MCIMX31RM       | 2.3     | MCIMX31 and MCIMX31L Application Processor RM              |

| MCIMX27RM       | 0.2     | MCIMX27 Multimedia Application Processor RM                |

| MC13783/D       | 3.4     | MC13783 Power Management and Audio Circuit Data Sheet      |

## 2.2 Acronyms

AD-TFT advanced thin film transistor (LCD technology)

AIC analog interface chips

ATA advanced technology attachment

BDM background debug mode BSP board support package

CF CompactFlash

CIR consumer infrared

CODEC coder/decoder

CPU central processing unit

CSI camera sensor interface

DC-DC direct current to direct current converter

DSI display serial interface

DSR data set ready

DTR data transmit ready

ETHER\_RX Ethernet receive signal

ETHER\_TX Ethernet transmit signal

FIR fast infrared

GPIO general purpose input or output

GPO general purpose output

HR-TFT high reflective thin film transistor (LCD technology)

i.MX27 SOM-LV (only used within the tables of this document) i.MX31 SOM-LV (only used within the tables of this document)

I2C Inter-integrated circuit busI2S Inter-integrated circuit sound

IO or I/O input/output signal

**IrDA** infrared data association

**IRQ** interrupt signal

JTAG joint test action group LCD liquid crystal display LDO low dropout regulator MAC medium access control

**MCBSP** multi-channel buffered serial port

MIR medium infrared MMC multi-media card

OMAPS OMAP35x SOM-LV (only used within the tables of this document)

**PCM** pulse code modulation

**PCMCIA** personal computer memory card international association

PHY physical layer device

**PMIC** power management integrated circuit

**RFBI** remote frame buffer interface

SD secure digital

TI Flatlink<sup>TM</sup>3G serial display interface SDI

SDIO secure digital input/output SIM subscriber identity module

SIR slow infrared SOC system-on-chip

SOM-LV low-voltage System on Module SPI

serial peripheral interface

STN super-twisted nematic (STN) or passive matrix LCD technology

TDM time division multiplexed

TFT thin film transistor (TFT) or active matrix LCD technology

**UART** universal asynchronous receiver/transmitter

uР microprocessor (see SOC)

#### 3 **General Features Overview**

This section gives a general feature set description of each SOM-LV module. Please refer to each module's Hardware Specification document for more detailed information about the physical specification requirements unique to that product.

Table 3.1: SOM-LV Comparison Overview

| Specifications            | i.MX31 SOM-LV                                                                      | i.MX27 SOM-LV                                                                      | OMAP35x SOM-LV                                                     |

|---------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Form Factor               | SOM-LV                                                                             | SOM-LV                                                                             | SOM-LV                                                             |

| Туре                      | Type I                                                                             | Type II                                                                            | Type III                                                           |

| Size                      | 59.1 x 76.2 x 7.9 mm                                                               | 50.8 x 76.2 x 7.9 mm                                                               | 31 x 76.2 x 7.4 mm                                                 |

| Available Software        | Microsoft Windows<br>Embedded CE Board<br>Support Packages (BSPs)                  | Microsoft Windows<br>Embedded CE BSPs                                              | Microsoft Windows<br>Embedded CE 6.0 BSPs<br>Open source Linux BSP |

| RoHS                      | RoHS compliant                                                                     | RoHS compliant                                                                     | RoHS compliant                                                     |

|                           | 0°C to 70°C<br>(commercial temp)<br>or<br>-30°C to 85°C                            | 0°C to 70°C<br>(commercial temp)<br>or<br>-20°C to 85°C                            | 0°C to 70°C<br>(commercial temp)<br>or<br>-40°C to 85°C            |

| Temp                      | (extended temp)                                                                    | (extended temp)                                                                    | (industrial temp)                                                  |

| ARM Core                  | ARM1136JF-S                                                                        | ARM926EJ-S                                                                         | Cortex-A8                                                          |

| Max Speed (MHz)           | up to 532                                                                          | up to 400                                                                          | up to 600                                                          |

| Available SDRAM (MB)      | 64, 128*                                                                           | 64, 128*                                                                           | 128*, 256                                                          |

| Available NAND Flash (MB) | 64                                                                                 | 64                                                                                 | 256*, 512                                                          |

| NOR Flash (MB)            | 2*, 4                                                                              | 2*, 4                                                                              | 0, 8*                                                              |

| Display                   | up to 800x600                                                                      | up to 800x600                                                                      | up to 1024x768                                                     |

| Touch Screen              | Integrated 4-wire touch screen controller (Freescale MC13783)                      | Integrated 4-wire touch screen controller (Freescale MC13783)                      | Integrated 4-wire touchscreen controller (TSC2004)                 |

| Serial Ports              | 3                                                                                  | 3                                                                                  | 3                                                                  |

| Audio                     | I2S compliant audio codec<br>(Freescale MC13783; 16-bit<br>stereo DAC, 13-bit ADC) | I2S compliant audio codec<br>(Freescale MC13783; 16-bit<br>stereo DAC, 13-bit ADC) | I2S compliant audio codec<br>(16-bit stereo DAC, 13-bit<br>ADC)    |

| USB 2.0                   | yes                                                                                | yes                                                                                | yes                                                                |

| USB OTG                   | yes                                                                                | yes                                                                                | yes                                                                |

| MMC/SD                    | yes                                                                                | yes                                                                                | yes                                                                |

| ATA                       | yes                                                                                | yes                                                                                | no                                                                 |

| TV Out                    | no                                                                                 | no                                                                                 | yes                                                                |

| CompactFlash Type 1       | yes                                                                                | yes                                                                                | memory-mode only                                                   |

| 10/100 Base-T Ethernet    | available                                                                          | yes                                                                                | available                                                          |

| 802.11b/g Ethernet        | no                                                                                 | no                                                                                 | available                                                          |

| Bluetooth                 | no                                                                                 | no                                                                                 | available                                                          |

<sup>\*</sup> Standard configuration

**available** indicates the feature is present on some standard configurations of the SOM but not others. Please review the Standard SOM Configurations tables available on each product's webpage for details: www.logicpd.com.

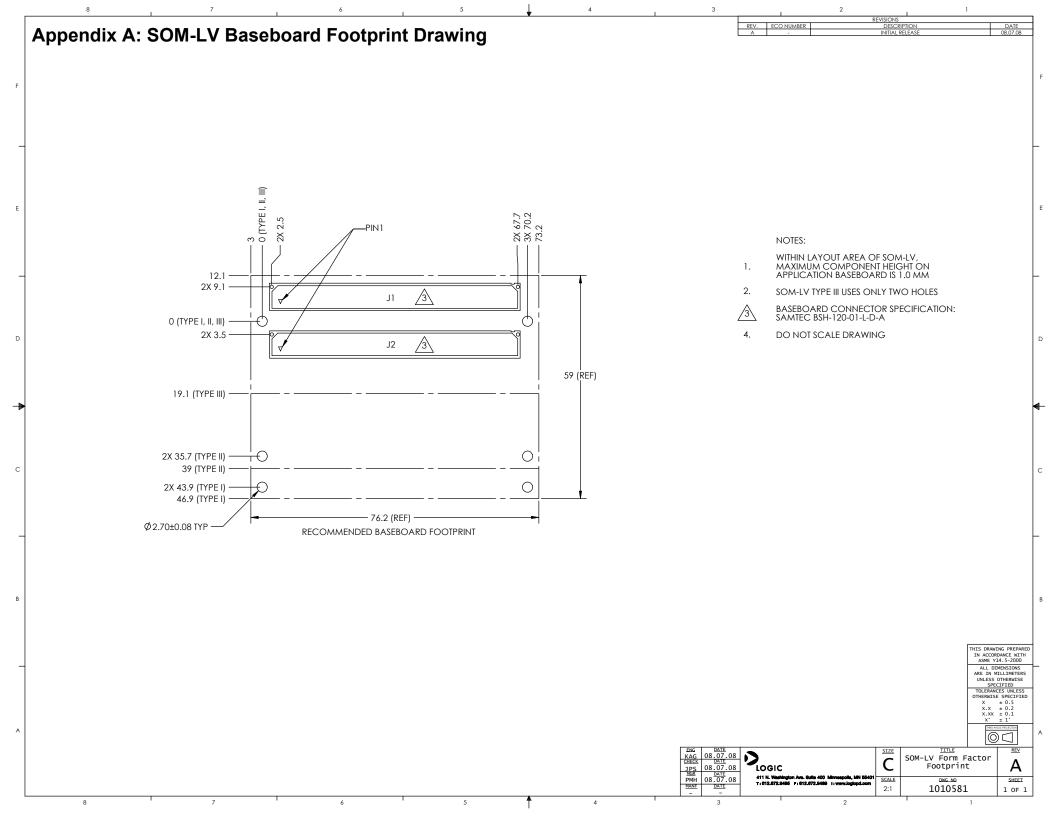

## 3.1 Mechanical Specifications

All three SOM-LV modules use the same physical J1 and J2 connectors to mate to a baseboard. As is evidenced in Table 3.1 above, the physical size of each module varies; as such, special care should be taken when designing your platform to mate with different SOM-LV Types. Appendix A, at the conclusion of this document, shows the recommended baseboard footprint for all three SOM-LV modules, including the different mounting hole locations. See *White Paper 340:* SOM-LV Mechanical Interface Specification for more detail information about the connectors and physical sizes of the SOM-LV form factor.

**Notes:** The mounting hole dimension may differ between the SOMs; however, all production-level SOM-LVs will have the same hole diameter of 2.70 mm. Please refer to each respective SOM-LV *Product Change Notification* (PCN) document to determine when the change was made for each product. (The i.MX31 SOM-LV has always had mounting hole diameters at 2.70 mm.)

## 4 Pin Comparison

Tables comparing pin usage between the i.MX27, i.MX31, and the OMAP35x SOM-LVs can be found in the Appendices of this document; Appendix B compares pins for the J1 connector, Appendix C compares pins for the J2 connector.

## 5 PMIC Information

Throughout this document, the power management and audio codec components may be referred to by their common names as specified in Table 5.1 below.

| Mfg Part # | Common Name | Description                                             |

|------------|-------------|---------------------------------------------------------|

|            |             | Integrated power management and audio codec used on the |

| MC13783    | Atlas       | i.MX31 and i.MX27 SOM-LVs                               |

|            |             | Integrated power management and audio codec used on the |

| TPS65950   | Triton2     | OMAP35x SOM-LV                                          |

Table 5.1: SOM-LV PMICs

## 6 Detailed Interface Descriptions

The specific interfaces discussed in this document have been grouped into the following categories:

- Power/Reset/Clock/PWM Control Signals

- Memory Interfaces

- Removable Media Interfaces

- Communication Interfaces

- Graphic Interfaces

## Notes about the tables used within this document:

- 1. Every attempt has been made to keep the tables readable at the default page magnification level. However, some tables will require you to use the Adobe Acrobat magnifying feature to properly view all the information.

- 2. Certain signals covered in this document may operate at different reference voltages on each SOM-LV module; therefore, these different voltages need to be called out within the tables describing those signals. To achieve this, signals are listed below the voltage domain in which they are located. Please see Table 6.1 below for an example of a table describing two signals in two different voltage domains. Notice that the CSPI3\_SCLK and CSPI3\_SS1 signals on the i.MX31 SOM-LV are on two different voltage domains (1.8V\_NVCC10 and 2.7V\_NVCC5/NVCC8 respectively). However, also notice that the similar signals on the i.MX27, CSPI3\_SCLK and CSPI3\_SS, both exist on the same voltage domain, VMMC1; this is indicated by the voltage domain field for the CSPI3\_SS stating "same as above".

Table 6.1: Example of Signals in Different Voltage Domains

|                   |               | i.N              | IX31 SOM- | LV        |         | i.MX27 SOM-LV |               |           |           |         |  |

|-------------------|---------------|------------------|-----------|-----------|---------|---------------|---------------|-----------|-----------|---------|--|

| SPI Signal        | SOM-LV Signal | i.MX31 Signal    | Primary   | J1/J2 Pin | Voltage | SOM-LV Signal | i.MX27 signal | Primary   | J1/J2 Pin | Voltage |  |

| Reference Voltage |               | SW2BOUT (BUCK) / |           |           |         |               | VMMC1(LDO) /  |           |           |         |  |

| Reg / Domain      | -             | 1.8V_NVCC10      | -         | -         | -       | -             | VMMC1         | -         | J2.138    | -       |  |

| SCLK              | uP_UARTC_CTS  | CSPI3_SCLK       | Alternate | J1.122    | 1.8     | SD1_CLK       | CSPI3_SCLK    | Alternate | J2.136    | -       |  |

| Reference Voltage |               | VRF1 (REG) /     |           | J1.152,   |         |               |               |           |           |         |  |

| Reg / Domain      | -             | 2.7V_NVCC5/NVCC8 | -         | J2.96     | 2.7     | -             | same as above | -         | -         | -       |  |

| CS0               | -             | -                | -         | -         | -       | SD1_DATA3     | CSPI3_SS      | Alternate | J2.124    | -       |  |

| CS1               | uP_CSPI2_SS1  | CSPI3_SS1        | Alternate | J2.89     | 2.7     | -             | -             | -         | -         | -       |  |

## 6.1 Power/Reset/Clock/PWM Control Signals

The i.MX31, i.MX27, and the OMAP35x SOM-LVs all use the nSTANDBY, nSUSPEND, and 3.3\_nEN control signals for power. All modules also have the same RESET control signals, such as uP\_SW\_nRESET, RESET\_nOUT, and MSTR\_nRST, with the same functionality. There are some control signals that are made available and are different from each module. See Table 6.2 for detailed differences.

Table 6.2: SOM-LV Power/Reset/Clock/PWM Interface

| PWR/RST/CLK      | SOM-LV                  | i.MX31 SOM                      | -LV       | i.MX27 SOM                      | -LV     | OMAP35x SON      | 1-LV                  |

|------------------|-------------------------|---------------------------------|-----------|---------------------------------|---------|------------------|-----------------------|

| Control Signal   | J1/J2 Pin               | SOM-LV Signal                   | Voltage   | SOM-LV Signal                   | Voltage | SOM-LV Signal    | Voltage               |

|                  |                         | F                               | Power Co  | ntrol Signals                   |         |                  |                       |

| PWR_ON           | J1.30                   | PWR_ON                          | 2.7       | PWR_ON                          | 2.7     | •                | -                     |

| nSTANDBY         | nSTANDBY J1.17 nSTANDBY |                                 |           | nSTANDBY                        | 2.7     | nSTANDBY         | 1.8                   |

| nSUSPEND         | J1.15                   | nSUSPEND                        | 2.7       | nSUSPEND                        | 2.7     | nSUSPEND         | 1.8                   |

| 3.3V_nEN         | J1.49                   | 3.3_nEN                         | 2.7       | 3.3_nEN                         | 2.7     | 3.3_nEN (DGND)   | 1.8 <sup>3</sup>      |

| VIBRA_M          | J2.75                   | -                               | -         | -                               | -       | VIBRA_M          | MAIN_BATT             |

| VIBRA_P          | J2.77                   | -                               | -         | -                               | -       | VIBRA_P          | MAIN_BATT             |

| RFID_EN          | J2.89                   | different function <sup>1</sup> | 2.7       | -                               | -       | RFID_EN          | Variable <sup>4</sup> |

| VAUX3            | J2.175                  | different function <sup>2</sup> | max 5.5   | different function <sup>2</sup> | max 5.5 | VAUX3            | Variable <sup>5</sup> |

| T2_REGEN         | J2.193                  | different function <sup>2</sup> | max 5.5   | different function <sup>2</sup> | max 5.5 | T2_REGEN         | MAIN_BATT             |

|                  |                         |                                 | Reset Cor | ntrol Signals                   |         |                  |                       |

| uP_SW_nRESET     | J1.223                  | uP_SW_nRESET                    | 2.7       | uP_SW_nRESET                    | 1.8     | uP_SW_nRESET     | 1.8                   |

| RESET_nOUT       | J1.225                  | RESET_OUT                       | 1.8       | RESET_OUT                       | 1.8     | RESET_OUT        | 1.8                   |

| MSTR_nRST        | J1.227                  | MSTR_nRST                       | 1.8       | MSTR_nRST                       | 1.8     | MSTR_nRST        | 1.8                   |

|                  |                         |                                 | Clock     | Signals                         |         |                  |                       |

| uP_AUX_CLK       | J1.28                   | uP_AUX_CLK                      | 1.8       | uP_AUX_CLK                      | 1.8     | •                | -                     |

| uP_CLKOUT1_26MHz | J2.233                  | -                               | -         | -                               | -       | uP_CLKOUT1_26MHz | 1.8                   |

| TWL_32K_CLK_OUT  | J2.234                  | -                               | -         | -                               | -       | TWL_32K_CLK_OUT  | 1.8                   |

|                  | -                       | -                               | PWM       | Signal                          | -       | -                | -                     |

| PWM0             | J1.168                  | PWM0                            | 2.7       | PWM0                            | 1.8     | PWM0             | 1.8                   |

- 1. i.MX31/RFID\_EN Signal name is uP\_CSPI2\_SS1 and can function as CSPI1\_SS3 or CSPI3\_SS1.

- 2. i.MX31/27 (J2.177/175) Signal function is LED Drive

- 3. OMAP35x/3.3\_nEN signal input is in the 1.8 voltage domain but its input is tied to DGND.

- 4. OMAP35x/RFID\_EN connects to the PMIC VMMC2.OUT Level

- 5. OMAP35x/VAUX3 connects to the PMIC VAUX3.OUT Level

## 6.2 Memory Interfaces

The available memory interfaces are the static memory bus interface and the ATA interface.

## 6.2.1 Static Memory Bus Interface

The i.MX31, i.MX27, and OMAP35x SOM-LVs route the 16-bit data bus with 25 address pins to the J1 connector. On the i.MX31 and i.MX27 SOM-LVs, the data bus (D15–D0) and the upper address lines (A24–A13) route directly to the processors, but the lower address lines (MA12–MA0) are buffered on both SOMs. On the OMAP35x SOM-LV, address lines (A16–A1) are latched using uP\_nADV\_ALE, while the remaining upper address lines (A26–A17) route directly to the processor.

The chip selects on all three SOMs have similarly defined functionality and have been routed to the same pins on the connectors.

The i.MX31 and OMAP35x SOM-LVs have two external DMA request pins. The i.MX27 SOM-LV does not support external DMA requests.

The OMAP35x general-purpose memory controller (GPMC) is the OMAP2 unified memory controller (UMC) dedicated to interfacing external memory devices:

- Asynchronous SRAM-like memories and application-specific integrated circuit (ASIC) devices;

- Asynchronous, synchronous, and page mode (only available in non-muxed mode) burst NOR flash devices;

- NAND flash;

- Pseudo-SRAM devices.

The i.MX27 and i.MX31 Wireless External Interface Memory Controller (WEIM) supports the following:

- 16-bit SRAM memories;

- 16-bit PSRAM (up to 133 MHz) memories;

- 16-bit NOR flash memories.

## Table 6.3: SOM-LV Memory Interface

|                                   | SOM-LV                                                                        | i.MX31                          | I SOM-LV         |         |                  | i.MX27 SOM-LV      |         | OMA                             | P35x SOM-LV      |         |

|-----------------------------------|-------------------------------------------------------------------------------|---------------------------------|------------------|---------|------------------|--------------------|---------|---------------------------------|------------------|---------|

| Memory Signal                     | J1/J2 Pin                                                                     | SOM-LV Signal                   | i.MX31 Signal    | Voltage | SOM-LV Signal    | i.MX27 signal      | Voltage | SOM-LV Signal                   | OMAP35x Signal   | Voltage |

|                                   | i.MX31S: -<br>i.MX27S: J1.183, J2.96,<br>J2.122                               |                                 |                  |         |                  |                    |         |                                 |                  |         |

| Reference Voltage                 | OMAPS: J1:110,144,152 /                                                       | SW2BOUT (BUCK) /                | NN 10010         |         | SW2BOUT (REG) /  | A11/DD4            | 4.0     | VIO.SW (REG) /                  | vdds             | 4.0     |

| Reg / Domain                      | J2:54,96,122                                                                  | 1.8V_NVCC10                     | NVCC10           | -       | DVDD_1.8V        | NVDD1              | 1.8     | VIO_1V8                         | vdds_mem         | 1.8     |

| BOOT_nCS                          | J2.172                                                                        | BOOT_nCS                        | CS0 <sup>1</sup> | 1.8     | BOOT_nCS         | CS0 <sup>1</sup>   | 1.8     | BOOT_nCS                        | GPMC_nCS2 1      | 1.8     |

| FLASH_nCS/NOR_nCS                 | on board flash                                                                | FLASH_nCS                       | CS0 <sup>1</sup> | 1.8     | FLASH_nCS        | CS0 <sup>1</sup>   | 1.8     | NOR_nCS                         | GPMC_nCS2 1      | 1.8     |

| EXT_BOOT_nSELECT                  | J2.168                                                                        | EXT_BOOT_nSELECT                | -                | 1.8     | EXT_BOOT_nSELECT | -                  | 1.8     | EXT_BOOT_nSELECT                | -<br>ODMO = 005  | 1.8     |

| SLOW_nCS/uP_nCS_A_EXT             | J1.145                                                                        | SLOW_nCS                        | CS5              | 1.8     | SLOW_nCS         | CS5                | 1.8     | uP_nCS_B_EXT                    | GPMC_nCS5        | 1.8     |

| BUFF_nOE_DATA                     | J1.121                                                                        | BUFF_nOE_DATA                   | -                | 1.8     | BUFF_nOE_DATA    | -                  | 1.8     | -                               | -                | -       |

| BUFF_DIR_DATA                     | J1.123                                                                        | BUFF_DIR_DATA                   | -                | 1.8     | BUFF_DIR_DATA    | -                  | 1.8     | BUFF_DIR_DATA                   | GPMC_IODIR       | 1.8     |

| D0                                | J1.40                                                                         | uP_D0                           | D0               | 1.8     | uP_D0            | D0                 | 1.8     | uP_D0                           | GPMC_D0          | 1.8     |

| D1                                | J1.42                                                                         | uP_D1                           | D1               | 1.8     | uP_D1            | D1                 | 1.8     | uP_D1                           | GPMC_D1          | 1.8     |

| D2                                | J1.44                                                                         | uP_D2                           | D2               | 1.8     | uP_D2            | D2                 | 1.8     | uP_D2                           | GPMC_D2          | 1.8     |

| D3                                | J1.46                                                                         | uP_D3                           | D3               | 1.8     | uP_D3            | D3                 | 1.8     | uP_D3                           | GPMC_D3          | 1.8     |

| D4                                | J1.48                                                                         | uP_D4                           | D4               | 1.8     | uP_D4            | D4                 | 1.8     | uP_D4                           | GPMC_D4          | 1.8     |

| D5                                | J1.50                                                                         | uP_D5                           | D5               | 1.8     | uP_D5            | D5                 | 1.8     | uP_D5                           | GPMC_D5          | 1.8     |

| D6                                | J1.54                                                                         | uP_D6                           | D6               | 1.8     | uP_D6            | D6                 | 1.8     | uP_D6                           | GPMC_D6          | 1.8     |

| D7                                | J1.56                                                                         | uP_D7                           | D7               | 1.8     | uP_D7            | D7                 | 1.8     | uP_D7                           | GPMC_D7          | 1.8     |

| D8                                | J1.58                                                                         | uP_D8                           | D8               | 1.8     | uP_D8            | D8                 | 1.8     | uP_D8                           | GPMC_D8          | 1.8     |

| D9                                | J1.60                                                                         | uP_D9                           | D9               | 1.8     | uP_D9            | D9                 | 1.8     | uP_D9                           | GPMC_D9          | 1.8     |

| D10                               | J1.62                                                                         | uP_D10                          | D10              | 1.8     | uP_D10           | D10                | 1.8     | uP_D10                          | GPMC_D10         | 1.8     |

| D11                               | J1.64                                                                         | uP_D11                          | D11              | 1.8     | uP_D11           | D11                | 1.8     | uP_D11                          | GPMC_D11         | 1.8     |

| D12                               | J1.66                                                                         | uP_D12                          | D12              | 1.8     | uP_D12           | D12                | 1.8     | uP_D12                          | GPMC_D12         | 1.8     |

| D13                               | J1.68                                                                         | uP_D13                          | D13              | 1.8     | uP_D13           | D13                | 1.8     | uP_D13                          | GPMC_D13         | 1.8     |

| D14                               | J1.70                                                                         | uP_D14                          | D14              | 1.8     | uP_D14           | D14                | 1.8     | uP_D14                          | GPMC_D14         | 1.8     |

| D15                               | J1.74                                                                         | uP_D15                          | D15              | 1.8     | uP_D15           | D15                | 1.8     | uP_D15                          | GPMC_D15         | 1.8     |

| uP_nADV_ALE                       | J2.87                                                                         | different function <sup>4</sup> | -                | -       | -                | -                  | -       | uP_nADV_ALE                     | GPMC_nADV_ALE    | 1.8     |

| uP_WP                             | J2.85                                                                         | different function <sup>6</sup> | -                | -       | -                | -                  | -       | uP_WP                           | GPMC_nWP         | 1.8     |

| Reference Voltage<br>Reg / Domain | i.MX31S: J1.110<br>i.MX27S: J2.122<br>OMAPS: J1:110,144,152 /<br>J2:54,96,122 | SW2AOUT (BUCK) /<br>1.8V_DDR    | NVCC2<br>NVCC22  | 1.8     | same as above    | NVDD2/NVDD3        | 1.8     | same as above                   | vdds<br>vdds_mem | 1.8     |

| uP_nCS_A_EXT                      | J1.143                                                                        | uP_nCS_A_EXT                    | CS1              | 1.8     | uP_nCS_A_EXT     | CS1_B              | 1.8     | uP_nCS_A_EXT                    | GPMC_nCS4        | 1.8     |

| uP_nCS_B_EXT                      | J1.141                                                                        | uP_nCS_B_EXT                    | CS3              | 1.8     | uP_nCS_B_EXT     | CS3_B/CSD1         | 1.8     | uP_nCS_B_EXT                    | GPMC_nCS5        | 1.8     |

| FAST_nCS/uP_nCS_A_EXT             | J1.147                                                                        | FAST_nCS                        | CS4 <sup>2</sup> | 1.8     | FAST_nCS         | CS4_B/ETMTRACESYNC | 1.8     | uP_nCS_A_EXT                    | GPMC_nCS4        | 1.8     |

| WRLAN_nCS                         | on board wrlan                                                                | WRLAN_nCS                       | CS4 <sup>2</sup> | 1.8     | -                | -                  | -       | uP_nCS1/uP_nMCS1                | GPMC_nCS1        | 1.8     |

| EB0                               | J1.137                                                                        | uP_EB0                          | EB0              | 1.8     | uP_nEB0          | EB0_B              | 1.8     | uP_nBE0                         | GPMC_nBE0_CLE    | 1.8     |

| EB1                               | J1.139                                                                        | uP_EB1                          | EB1              | 1.8     | uP_nEB1          | EB1_B              | 1.8     | uP_nBE1                         | GPMC_nBE1        | 1.8     |

| OE                                | J1.125                                                                        | uP_OE                           | OE               | 1.8     | uP_nOE           | OE_B               | 1.8     | uP_nOE                          | GPMC_nOE         | 1.8     |

| RW                                | J1.127                                                                        | uP_RnW                          | RW               | 1.8     | uP_RnW           | RW_B               | 1.8     | uP_nWE                          | GPMC_nWE         | 1.8     |

| LBA                               | J2.14                                                                         | uP_nLBA                         | LBA              | 1.8     | uP_nLBA          | LBA_B              | 1.8     | different function <sup>5</sup> | -                | 1.8     |

| BCLK                              | J1.131                                                                        | uP_BUS_CLK                      | BCLK             | 1.8     | uP_BUS_CLK       | BCLK               | 1.8     | uP_BUS_CLK                      | GPMC_CLK         | 1.8     |

| ECB/WAIT                          | J1.109                                                                        | uP nWAIT                        | ECB              | 1.8     | uP nWAIT         | ECB_B              | 1.8     | uP_nWAIT                        | GPMC_WAIT1       | 1.8     |

| A0                                | J1.53                                                                         | DGND                            | DGND             | DGND    | DGND             | DGND               | DGND    | DGND                            | -                | DGND    |

| A1                                | J1.55                                                                         | uP MA0                          | A0               | 1.8     | uP MA0           | A0 <sup>3</sup>    | 1.8     | uP LA1                          | GPMC D0          | 1.8     |

| A2                                | J1.57                                                                         | uP MA1                          | A1               | 1.8     | uP MA1           | A1 <sup>3</sup>    | 1.8     | uP LA2                          | GPMC D1          | 1.8     |

| A3                                | J1.59                                                                         | uP MA2                          | A2               | 1.8     | uP MA2           | A2 <sup>3</sup>    | 1.8     | uP LA3                          | GPMC D2          | 1.8     |

| A4                                | J1.61                                                                         | uP MA3                          | A3               | 1.8     | uP MA3           | A3 <sup>3</sup>    | 1.8     | uP LA4                          | GPMC D3          | 1.8     |

| A5                                | J1.63                                                                         | uP MA4                          | A4               | 1.8     | uP MA4           | A4 <sup>3</sup>    | 1.8     | uP LA5                          | GPMC D4          | 1.8     |

| A6                                | J1.65                                                                         | uP_MA5                          | A5               | 1.8     | uP_MA5           | A5 <sup>3</sup>    | 1.8     | uP_LAS<br>uP LA6                | GPMC_D4  GPMC D5 | 1.8     |

|                                   |                                                                               |                                 |                  |         | _                |                    |         | _                               |                  |         |

| A7                                | J1.67                                                                         | uP_MA6                          | A6               | 1.8     | uP_MA6           | A6 <sup>3</sup>    | 1.8     | uP_LA7                          | GPMC_D6          | 1.8     |

Table 6.3: SOM-LV Memory Interface (continued)

|                   | SOM-LV                             | i.MX3            | 1 SOM-LV      |         |               | i.MX27 SOM-LV    |         | OMA           | AP35x SOM-LV   |         |

|-------------------|------------------------------------|------------------|---------------|---------|---------------|------------------|---------|---------------|----------------|---------|

| Memory Signal     | J1/J2 Pin                          | SOM-LV Signal    | i.MX31 Signal | Voltage | SOM-LV Signal | i.MX27 signal    | Voltage | SOM-LV Signal | OMAP35x Signal | Voltage |

|                   | i.MX31S: J1.110<br>i.MX27S: J2.122 |                  |               |         |               |                  |         |               |                |         |

| Reference Voltage |                                    | SW2AOUT (BUCK) / | NVCC2         |         |               |                  |         |               | vdds           |         |

| Reg / Domain      | J2:54,96,122                       | 1.8V_DDR         | NVCC22        | 1.8     | same as above | NVDD2/NVDD3      | 1.8     | same as above | vdds_mem       | 1.8     |

| A8                | J1.69                              | uP_MA7           | A7            | 1.8     | uP_MA7        | A7 <sup>3</sup>  | 1.8     | uP_LA8        | GPMC_D7        | 1.8     |

| A9                | J1.73                              | uP_MA8           | A8            | 1.8     | uP_MA8        | A8 <sup>3</sup>  | 1.8     | uP_LA9        | GPMC_D8        | 1.8     |

| A10               | J1.75                              | uP_MA9           | A9            | 1.8     | uP_MA9        | A9 <sup>3</sup>  | 1.8     | uP_LA10       | GPMC_D9        | 1.8     |

| A11               | J1.77                              | uP_MA10          | A10           | 1.8     | uP_MA10       | A10 <sup>3</sup> | 1.8     | uP_LA11       | GPMC_D10       | 1.8     |

| A12               | J1.79                              | uP_MA11          | A11           | 1.8     | uP_MA11       | A11 <sup>3</sup> | 1.8     | uP_LA12       | GPMC_D11       | 1.8     |

| A13               | J1.81                              | uP_MA12          | A12           | 1.8     | uP_MA12       | A12 <sup>3</sup> | 1.8     | uP_LA13       | GPMC_D12       | 1.8     |

| A14               | J1.83                              | uP_A13           | A13           | 1.8     | uP_A13        | A13 <sup>3</sup> | 1.8     | uP_LA14       | GPMC_D13       | 1.8     |

| A15               | J1.85                              | uP_A14           | A14           | 1.8     | uP_A14        | A14 <sup>3</sup> | 1.8     | uP_LA15       | GPMC_D14       | 1.8     |

| A16               | J1.87                              | uP_A15           | A15           | 1.8     | uP_A15        | A15 <sup>3</sup> | 1.8     | uP_LA16       | GPMC_D15       | 1.8     |

| A17               | J1.89                              | uP_A16           | A16           | 1.8     | uP_A16        | A16 <sup>3</sup> | 1.8     | uP_A1         | GPMC_A1        | 1.8     |

| A18               | J1.93                              | uP A17           | A17           | 1.8     | uP A17        | A17 <sup>3</sup> | 1.8     | uP A2         | GPMC_A2        | 1.8     |

| A19               | J1.95                              | uP A18           | A18           | 1.8     | uP A18        | A18 <sup>3</sup> | 1.8     | uP A3         | GPMC A3        | 1.8     |

| A20               | J1.97                              | uP A19           | A19           | 1.8     | uP A19        | A19 <sup>3</sup> | 1.8     | uP A4         | GPMC A4        | 1.8     |

| A21               | J1.99                              | uP A20           | A20           | 1.8     | uP A20        | A20 <sup>3</sup> | 1.8     | uP_A5         | GPMC A5        | 1.8     |

| A22               | J1.101                             | uP A21           | A21           | 1.8     | uP A21        | A21 <sup>3</sup> | 1.8     | uP A6         | GPMC A6        | 1.8     |

| A23               | J1.103                             | uP A22           | A22           | 1.8     | uP A22        | A22 <sup>3</sup> | 1.8     | uP A7         | GPMC_A7        | 1.8     |

| A24               | J1.105                             | uP A23           | A23           | 1.8     | uP_A23        | A23 <sup>3</sup> | 1.8     | uP A8         | GPMC A8        | 1.8     |

| A25               | J1.107                             | uP A24           | A24           | 1.8     | uP A24        | A24 <sup>3</sup> | 1.8     | uP_A9         | GPMC A9        | 1.8     |

| A26               | J2.56                              | uP A25           | A25           | 1.8     | uP A25        | A25 <sup>3</sup> | 1.8     | uP A10        | GPMC A10       | 1.8     |

| D16               | J1.76                              | -                | -             | -       | -             | _                | -       | -             |                | -       |

| D17               | J1.78                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D18               | J1.80                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D19               | J1.82                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D20               | J1.84                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D21               | J1.86                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D22               | J1.88                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D23               | J1.90                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D24               | J1.94                              | -                | -             | -       | -             |                  | -       | -             | -              | -       |

| D25               | J1.96                              | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D26               | J1.98                              | -                | -             | -       | -             |                  | -       | -             | -              | -       |

| D27               | J1.100                             | -                | -             | -       | -             | -                | -       | -             |                | -       |

| D28               | J1.102                             | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D29               | J1.104                             | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D30               | J1.106                             | -                | -             | -       | -             | -                | -       | -             | -              | -       |

| D31               | J1.108                             | -                | -             |         | -             | -                | -       | -             | -              | -       |

| Reference Voltage |                                    | VIOLO (Reg) /    | NIV.CC7       | 4.0     | -             | -                | -       | sama aa ahaya | vdds           | 4.0     |

| Reg / Domain      | J2:54,96,122                       | 1.8V_NVCC7       | NVCC7         | 1.8     |               |                  |         | same as above | vdds_mem       | 1.8     |

| uP_DREQ0          | J1.133                             | uP_DREQ0         | EXTDMA_0      | -       | -             | -                | -       | uP_DREQ0      | SYS_nDMAREQ3   | 1.8     |

| uP_DREQ1          | J1.135                             | uP_DREQ1         | EXTDMA_1      |         | -             | -                | -       | uP_DREQ1      | SYS_nDMAREQ1   | 1.8     |

- 1. See information on EXT\_BOOT\_nSELECT in the SOM-LV Hardware Specification Manual for select of nCS.

- 2. See information on FAST\_nCS and WRLAN\_nCS in the i.MX31 SOM-LV Hardware Specification Manual.

- 3. Signal is buffered.

- 4. i.MX31/uP\_nADV\_ALE Signal function is CSPI2\_SS2/I2C3\_SDA/IPU\_FLS\_STRB and voltage domain for this signal is 2.7V\_NVCC5/NVCC8.

- 5. OMAP35x Signal Function is uP\_nOE. This is the same function with regards to the PCMCIA/CF, but does not function as the LBA as on the i.MX31.

- 6. i.MX31/uP\_WP Signal function is uP\_CSPI2\_RDY, not useful for the i.MX31.

#### 6.2.2 ATA Interface

The ATA interface is muxed behind different interfaces on the i.MX31 and i.MX27 processors; the OMAP35x does not have an ATA controller. On the i.MX31 SOM-LV, the ATA interface is shared with the camera interface, PWM0, Keypad, and I2C port 1; on the i.MX27 SOM-LV, the ATA interface is shared with the Ethernet MAC interface to the PHY and the PCMCIA control signals. This sharing makes these interfaces mutually exclusive on the SOMs. See Table 6.4 below for the ATA interface common pins on the SOMs.

Table 6.4: SOM-LV ATA Interface

|                             | SOM-LV                  | i.MX3                       | 1 SOM-LV    |         | i.MX27 Sc                | OM-LV         |         |

|-----------------------------|-------------------------|-----------------------------|-------------|---------|--------------------------|---------------|---------|

| ATA Signal                  | J1/J2 Pin               | SOM-LV Signal               | uP Signal   | Voltage | SOM-LV Signal            | uP Signal     | Voltage |

|                             | i.MX31S: J2.54, J2.80   |                             |             |         |                          |               |         |

| Reference Voltage           | i.MX27S: J1.183, J2.96, | VMMC2 (LDO) /               |             |         | SW2BOUT (REG) /          |               |         |

| Reg / Domain                | J2.122                  | NVCC3                       | NVCC3       | 2.8     | DVDD_1.8V                | NVDD5         | 1.8     |

| ATA_RESET                   | J2.59                   | ATA_RESET                   | ATA_RESET_B | 2.8     | uP_PCC_RESET/ATA_nRESET  | ATA_RESET_B   | 1.8     |

| ATA_DIOR                    | J2.65                   | CSI_D2                      | ATA_DIOR    | 2.8     | uP_PCC_CD1/ATA_DIOR      | ATA_DIOR      | 1.8     |

| ATA_DIOW                    | J2.63                   | CSI_D3                      | ATA_DIOW    | 2.8     | uP_PCC_CD2/ATA_DIOW      | ATA_DIOW      | 1.8     |

| ATA_CS1                     | J2.67                   | CSI_D1                      | ATA_CS1     | 2.8     | uP_PCC_nWAIT/ATA_CS1     | ATA_CS1       | 1.8     |

| ATA_CS0                     | J2.69                   | CSI_D0                      | ATA_CS0     | 2.8     | uP_PCC_RDYA/ATA_CS0      | ATA_CS0       | 1.8     |

| ATA_DMACK                   | J2.61                   | ATA_DMACK                   | ATA_DMACK   | 2.8     | uP_PCC_BVD2_DMACK        | ATA_DMACK     | 1.8     |

| ATA_IORDY                   | J2.57                   | PWM0                        | ATA_IORDY   | 2.8     | uP_PCC_RESET/ATA_nRESET  | ATA_IORDY     | 1.8     |

|                             | i.MX31: J2.122          |                             |             |         |                          |               |         |

| Reference Voltage           | i.MX27S: J1.183, J2.96, | VRF1 (REG) /                |             |         |                          |               |         |

| Reg / Domain                | J2.122                  | 2.7V_NVCC6/NVCC9            | NVCC6       | 2.7     | same as above            | NVDD5         | 1.8     |

| ATA_DA2                     | J2.93                   | PCC_PCMCIA_nEN <sup>2</sup> | ATA_DA2     | 2.7     | PC_PWRON/ATA_DA2         | ATA_DA2       | 1.8     |

| ATA_DA1                     | J2.95                   | KEY_COL6                    | ATA_DA1     | 2.7     | uP_PCC_VS1/ATA_DA1       | ATA_DA1       | 1.8     |

| ATA_DA0                     | J2.97                   | KEY_COL5                    | ATA_DA0     | 2.7     | uP_PCC_VS2/ATA_DA0       | ATA_DA0       | 1.8     |

| ATA_DMARQ                   | J2.99                   | KEY_COL4                    | ATA_DMARQ   | 2.7     | uP_PCC_BVD1/ATA_DMARQ    | ATA_DMARQ     | 1.8     |

| ATA INTRQ                   | J2.113                  | KEY ROW6                    | ATA INTRQ   | 2.7     | uP PCC nIOIS16/ATA INTRQ | ATA INTRQ     | 1.8     |

| ATA_BUFFER_DIR <sup>1</sup> | J2.109                  | KEY ROW7                    | ATA BUF EN  | 2.7     | uP_PC_POE/ATA_BUFFER_EN  | ATA_BUFFER_EN | 1.8     |

|                             | i.MX31S: J1.144, J2.173 | _                           |             |         |                          |               |         |

| Reference Voltage           | i.MX27S: J1.183, J2.96, | VCAM (REG) /                |             |         |                          |               |         |

| Reg / Domain                | J2.122                  | NVCC4                       | NVCC4       | 2.8     | same as above            | NVDD6         | 1.8     |

| ATA_DATA0                   | J2.55                   | CSI_D6                      | ATA_D0      | 2.8     | uP_ATA_D0                | ATA_D0        | 1.8     |

| ATA DATA1                   | J2.53                   | CSI_D7                      | ATA D1      | 2.8     | uP ATA D1                | ATA D1        | 1.8     |

| ATA DATA2                   | J2.49                   | CSI D8                      | ATA_D2      | 2.8     | uP_ATA_D2                | ATA_D2        | 1.8     |

| ATA DATA3                   | J2.47                   | CSI D9                      | ATA D3      | 2.8     | uP ATA D3                | ATA D3        | 1.8     |

| ATA DATA4                   | J2.45                   | CSI D10                     | ATA D4      | 2.8     | uP ATA D4                | ATA D4        | 1.8     |

| ATA DATA5                   | J2.43                   | CSI D11                     | ATA D5      | 2.8     | uP ATA D5                | ATA D5        | 1.8     |

| ATA_DATA6                   | J2.41                   | CSI_D12                     | ATA_D6      | 2.8     | uP_ATA_D6                | ATA_D6        | 1.8     |

| ATA DATA7                   | J2.39                   | CSI D13                     | ATA D7      | 2.8     | uP_ATA_D7                | ATA D7        | 1.8     |

| ATA DATA8                   | J2.37                   | CSI D14                     | ATA D8      | 2.8     | uP ATA D8                | ATA_D8        | 1.8     |

| ATA_DATA9                   | J2.35                   | CSI D15                     | ATA D9      | 2.8     | uP_ATA_D9                | ATA D9        | 1.8     |

| ATA DATA10                  | J2.33                   | CSI MCLK                    | ATA D10     | 2.8     | uP ATA D10               | ATA D10       | 1.8     |

| ATA DATA11                  | J2.29                   | CSI VSYNC                   | ATA D11     | 2.8     | uP ATA D11               | ATA D11       | 1.8     |

| ATA_DATA12                  | J2.27                   | CSI_HSYNC                   | ATA_D12     | 2.8     | uP_ATA_D12               | ATA_D12       | 1.8     |

| ATA DATA13                  | J2.25                   | CSI PCLK                    | ATA D13     | 2.8     | uP ATA D13               | ATA D13       | 1.8     |

| ATA DATA14                  | J2.23                   | I2C1 CLK                    | ATA D14     | 28      | uP ATA D14               | ATA D14       | 1.8     |

| ATA DATA15                  | J2.21                   | I2C1 DATA                   | ATA D15     |         | uP_ATA_D15               | ATA D15       | 1.8     |

<sup>1.</sup> An optional 74xxx245 bus transceiver can be placed between the host side of the data bus and the device side of the data bus. If the transceiver is used, its enable should be tied low (always enable) and its direction pin should be tied to ATA\_BUFFER\_EN in such a way that it drives from host to device when ATA\_BUFFER\_EN is high and drives from device to host when ATA\_BUFFER\_EN is low.

<sup>2.</sup> ATA and PCMCIA/CF cannot co-exist.

#### 6.3 Removable Media Interfaces

Three removable media interface types exist for each SOM-LV: PCMCIA/CF, MMC/SD, and SIM. The following sections will cover these interfaces in more detail.

## 6.3.1 PCMCIA/CF Card Interface

The i.MX31 and i.MX27 SOM-LVs bring all the PCMCIA/CF control signals down to the baseboard and support I/O, memory, and attribute accesses to PCMCIA and CompactFlash cards. Both SOMs can support simultaneous use of PCMCIA and CompactFlash cards, as long as only one card requires access to memory-only space.

The OMAP35x SOM-LV only supports memory-only accesses to a single PCMCIA or CompactFlash card.

The host controller for the i.MX31 and i.MX27 supports the following specifications:

- PCMCIA

- □ Support for PCMCIA Rel 2.1

- □ CompactFlash

- □ PC Card

- □ TrueID Mode

Below is a table that shows the routing of the signals required depending on the desired card and the desired access of the target card being used.

Table 6.5: SOM-LV PCMCIA/CompactFlash Card Interface

| CF Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SOM-LV<br>J1/J2 Pin<br>31S: J2.54, J2.80<br>IX27S: J1.110<br>OMAPS:<br>:110,144,152 /<br>I2:54,96,122<br>J2.36<br>J2.26<br>J2.24<br>J2.34<br>J2.16<br>J2.46 | (I/O & Memory)<br>i.MX Only | (Memory Only)<br>i.MX Only | (Memory Only)<br>OMAP35x | SOM LV Sign of   |           |         |                 |           |         |                |            |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|--------------------------|------------------|-----------|---------|-----------------|-----------|---------|----------------|------------|---------|

| I.MX31S: J   i.MX31S: J   i.MX27S   OM   J1:110,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31S: J2.54, J2.80<br>IX27S: J1.110<br>OMAPS:<br>:110,144,152 /<br>I2:54,96,122<br>J2.36<br>J2.26<br>J2.24<br>J2.34<br>J2.16                                 | i.MX Only                   | i.MX Only                  | OMAP35x                  | COM LV Cincol    |           |         |                 |           |         |                |            |         |

| I.MX27S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MX27S: J1.110<br>OMAPS:<br>:110,144,152 /<br>J2:54,96,122<br>J2:36<br>J2:26<br>J2:24<br>J2:34<br>J2:16                                                      |                             |                            |                          | SOM-LV Signal    | uP Signal | Voltage | SOM-LV Signal   | uP Signal | Voltage | SOM-LV Signal  | uP Signal  | Voltage |

| I.MX27S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MX27S: J1.110<br>OMAPS:<br>:110,144,152 /<br>J2:54,96,122<br>J2:36<br>J2:26<br>J2:24<br>J2:34<br>J2:16                                                      |                             |                            |                          |                  |           |         |                 |           |         |                |            |         |

| Reference Voltage Reg / Domain Reg / Domain J2:54, PCC_nDRV_nEN J2:92, PCC_CD1 J2 PCC_CD2 J2 PCC_RESET J2 READY INIOIS16 J2 BVD1 J2 BVD2 VS1 VS2 INWAIT J2 REference Voltage Reg / Domain J2:54, NOE J2:54, NOE J2:54, NOE J2:54, NOE J2:54, NOE J2:54, NOE J3:54, NOE J | OMAPS:<br>:110,144,152 /<br>J2:54,96,122<br>J2:36<br>J2:26<br>J2:24<br>J2:34<br>J2:16                                                                       |                             |                            |                          |                  |           |         |                 |           |         |                |            |         |

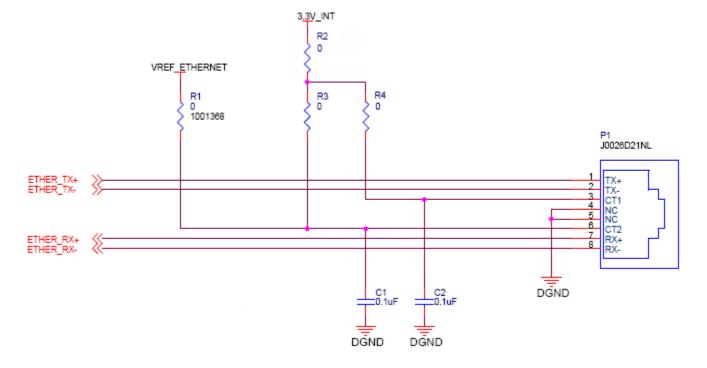

| Reference Voltage         J1:110, Reg / Domain         J2:54, PCC_nDRV_nEN         J2:54, PCC_nDRV_nEN         J2:54, PCC_nDRV_nEN         J2:54, PCC_nDRV_nEN         J2:54, PCC_nDRV_nEN         J2:10, PCC_nDRV_nEN         J2:11, PCC_nDRV_nEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | :110,144,152 /<br>J2:54,96,122<br>J2:36<br>J2:26<br>J2:24<br>J2:34<br>J2:16                                                                                 |                             |                            |                          |                  |           |         |                 |           |         |                |            |         |